一種視頻合成方法

摘要:為了在接口有限的CPU中傳輸多路視頻數字信號,介紹了一種視頻合成方法,通過FPGA把4路BT.656標準D1格式的視頻信號合成為1路BT.656 D1格式的視頻信號。A/D轉換以后的視頻信號是標準D1格式的數字視頻信號,FPGA產生讀寫信號控制雙口RAM讀寫操作,先把D1格式的數字視頻信號存進雙口RAM,然后分時地讀取4個RAM,把每路D1格式的數字視頻信號縮小為CIF格式的數字視頻信號,產生1個新的遵循BT.656標準的D1格式的視頻信號。實踐證明,此方法能有效地完成視頻合成,達到設計要求。

關鍵詞:視頻合成;BT.656;FPGA;數字視頻

在很多視頻應用場景中,需要用到多路數字視頻信號。一些視頻微處理器的輸入輸出接口有限,無法傳輸多路數字視頻信號,故對視頻信號進行合成傳輸是一件十分有意義的事情,通用的做法是通過可編程邏輯器件進行合成。鑒于此,本文利用ITU—RBT.656特有的幀結構,論述了把4路ITU—R BT.656數字視頻信號合成為1路ITU—R BT.656數字視頻信號的方法。

1 系統設計方案

1.1 硬件框架

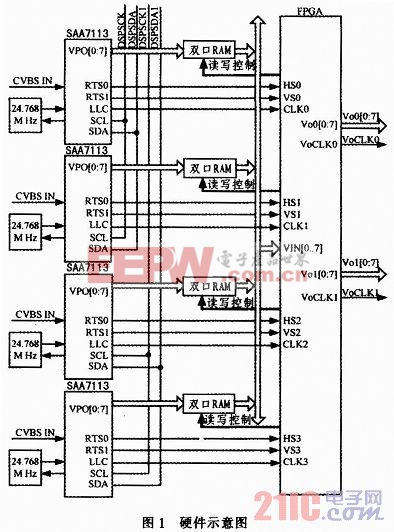

本設計通過FPGA實現4路ITU—R BT.656 D1格式的數字視頻信號在1路視頻通道中傳輸,在視頻解碼器(SAA7113)輸出口與CPU的視頻輸入口之間增加了耦合合成邏輯,利用FPGA實現二者之間的耦合。硬件連接圖如圖1所示,FPGA與SAA7113通過雙口RAM耦合,FPGA控制雙口RAM的讀寫邏輯,分時地讀取4個雙口RAM中的數據,數字視頻信號在FPGA里面進行合成。

SAA7113外部時鐘源由24.768 M的晶體提供,內部PLL產生SAA7113所需要的工作時鐘,VPO輸出時鐘頻率是27 MHz。SAA7113的初始化由CPU通過兩組I2C總線完成,每組的2個SAA7113使用不同的I2C從地址(通過設置RTS0)。4路模擬CVBS信號分別輸入4片SAA7113的AI22.4片SAA7113的VPO總線分別連接到4個雙口RAM的輸入端,SAA7113的RTS0、RTS1、LLC連接到FPGA,FPGA根據視頻同步信息控制雙口RAM的讀寫時序,雙口RAM的數據輸出端以總線形式連接到FPGA。

1.2 主要器件選型

系統采用SAA7113作為A/D轉換器件。SAA7113是一款視頻解碼芯片,通過配置內部寄存器可對4路模擬輸入視頻信號進行選擇,輸入信號可為4路CVBS或2路S視頻(Y/C)信號,輸出8位總線,為標準的ITU—R BT.656 YUV 4:2:2格式視頻流,可以配置為10位模式。7113支持PAL、NTSC、SECAM多種制式,可在PAL、NTSC之間自動轉換,自動檢測場頻(50 Hz或60 Hz)。對色度、亮度等的控制都是通過對相應寄存器寫入不同的配置值來實現,寄存器的讀寫通過I2C總線進行。

本設計利用SAA7113 LLC時鐘輸出時鐘信號27 MHz作為FPGA輸入時鐘源,利用片內PLL對其進行倍頻,作為FPGA全局時鐘使用,復位使用上電復位。

FPGA采用Xilinx公司的大容量、低成本、低功耗Spartan-3E系列XC3S250E。Spartan-3E家族優勢主要是系統連接功能(包括物理并行I/O接口)和高帶寬所需要的協議。Spartan-3E器件I/O管腳支持全部的SelectIO。支持18種通用I/O接口標準(PCI 64/66、PCI—X 100、RSDS和mini—LVDS等),以及普通DDR存儲接口。提供每秒高達91億次的乘累加(MAC)。內置18x18嵌入式乘法器可用來實現緊密的DSP結構(比如MAC引擎及自適應、全并行FIR濾波器)。SRL16移位寄存器邏輯和分布式存儲器可用來實現高密度DSP結構,比如濾波器。其內核電壓為12V和2.5 V,IO電壓為3.3V。XC3S250E能提供25萬個等效邏輯門,本產品選擇PQ208封裝,能夠提供158個用戶可用的輸入/輸出管腳。

在本設計中,XC3S250E的配置采用Slave Serial模式(M[2:0]=“111”),通過CPU把FPGA的配置數據通過同步串行接口寫入FPGA。CPU使用GPIO管腳來模擬FPGA的串行配置時序。

為了方便FPGA的調試,在電路板上預留JTAG配置接口。

本設計需要對4路720x576的視頻數據進行存儲,每路存儲空間為576行x720x2字節(在4:2:2的YCbCr信號中,一個點實際占用2字節(用亮度色差表示))。因此每路需要800 kB左右的存儲空間。在設計中使用了4片1 MB容量的雙口SRAM,用于緩存4路視頻數據。

對FPGA模塊,輸入的5.0 V經1片TPS76833轉換為3.3V,供FPGA VCCO使用。5.0V經1片RT8011變換后輸出+2.6V/2A的電壓,一路提供給XC3S250E的VCCAUX使用:另一路由RT9183 LDO變換為+1.2V/1.5A電壓,為XC3S250E內核供電。輸入的5.0V經一片TPS76833轉換為3.3V,為其他器件供電。

2 視頻合成描述

本文描述針對PAL制式,視頻合成的具體實現思路為:4通道數據分別在水平方向/垂直方向各縮小1/2(由D1格式縮小為CIF格式):將4個CIF格式的數字視頻流拼接成1個ITU—R BT.656數字視頻流,和CPU(DSP)的視頻口連接。通過FPGA對4路SAA7113輸入數據的合成,可以同時傳送4路352x288像素的視頻信號。

模擬CVBS信號輸入以后,經過相關處理(鉗位、幅度放大、抗混疊濾波、A/D轉換、YUV分離)電路之后,轉換為BT.656 D的頻數據流,從SAA7113輸出的視頻數據源是分辨率為720x576 D1格式的視頻源。分辨率為720x576,每幀625行,每行1728個像素點。正好可以分割為4路252x288像素的視頻源,多余空間通過數據8010來填充。

首先配置SAA7113相關寄存器,把RTS0、RTS1配置為HS、VS,FPGA根據HS、VS的時序關系并利用片內計數器對BT656數據流進行幀同步檢測,找到準確的同步信息,確定定時信息。然后啟動雙口RAM寫操作(寫RAM地址與BT656的行場時序嚴格對應,約定一種映射關系,方便讀操

作),再根據定時信息控制雙口RAM讀時序,把4路雙口RAM讀出端的數據線以總線方式連接在一起,FPGA分時地讀取不同的RAM模塊。4個RAM輸給FPGA的數據是連續的,它們分時地來自不同的模塊,填充到對應的區域,原來存放第一場數據的位置用來存放第1、第2路視頻源,原來存放第二場數據的位置用來存放第3、第4路視頻源,同時插入ITU—R BT.656幀格式的同步信息,其他位置插入固定數據8010,產生一路符合ITU—R BT.656標準的D1格式的數字視頻流。

經過合成處理以后,FPGA可以為CPU提供1路符合ITU—R BT.656 D1格式的視頻數據流。

3 實驗分析及結語

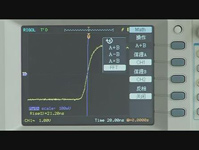

對系統性能進行了較為完備的測試,通過視頻編碼器對輸入合成視頻數據進行測試。為了測試設計達到預定要求,選用了多種視頻輸入源進行測試,有測試運動快慢及劇烈程度的畫面,有測試黑白圖像效果的全黑與全白,還有測試亮度等級的階梯圖案等等。

實驗結果表明,在4路D1圖像輸入時,平均信躁比達到33 dB以上,能實時地進行編碼,解碼圖像畫面清晰流暢,沒有馬賽克以及動畫現象,色彩鮮艷,亮度分明。

本文論述了一種4路D1視頻流合成1路D1格式視頻流的方法,此設計完全能滿足特定條件下的多路視頻數據傳輸,符合實際應用場景,達到設計要求。

評論