IEEE1588在分散運動控制系統中的應用

引言

本文說明IEEE1588在一個分散運動控制系統中的應用,目前的解決方案依靠分散運動部件對時間同步的專門實現。隨著IEEE1588的出現,可以開發一種在標準網絡(如以太網)上使用商用技術的運動控制解決方案。本文要說明在一個網絡范例內IEEE1588和運動的基本操作。

分散運動控制要求系統節點之間緊密地同步,通常這要求在系統內時鐘間的波動是微秒數量級。更高性能的應用驅動將這個性能提高到幾分一微秒范圍。當前的解決方案是使用適當的網絡和接口部件達到使分散系統內節點間的緊密同步。定制的接口卡控制整個系統時鐘的分配和同步以及控制數據的定時傳送。

IEEE1588精確時間協議提供分布網絡上的標準化的同步機制,通過使用IEEE1588協議就可在標準網絡上用標準化的解決方案取代專用解決方案。就可用現成的部件代替專用的網絡接口部件。

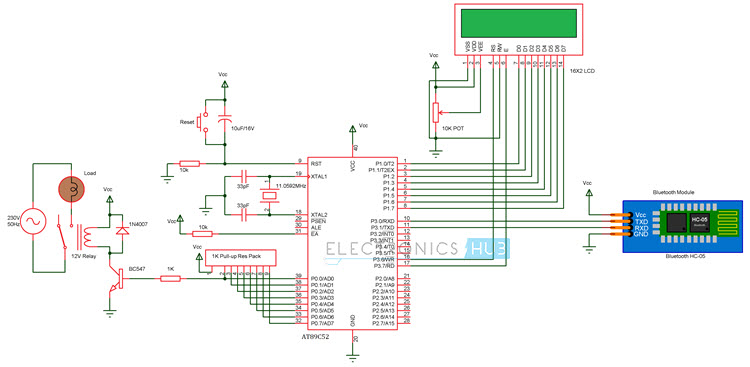

現使用IEEE1588協議和以太網實現一個簡單的分布運動控制系統,用以演示這個原理。

范例說明

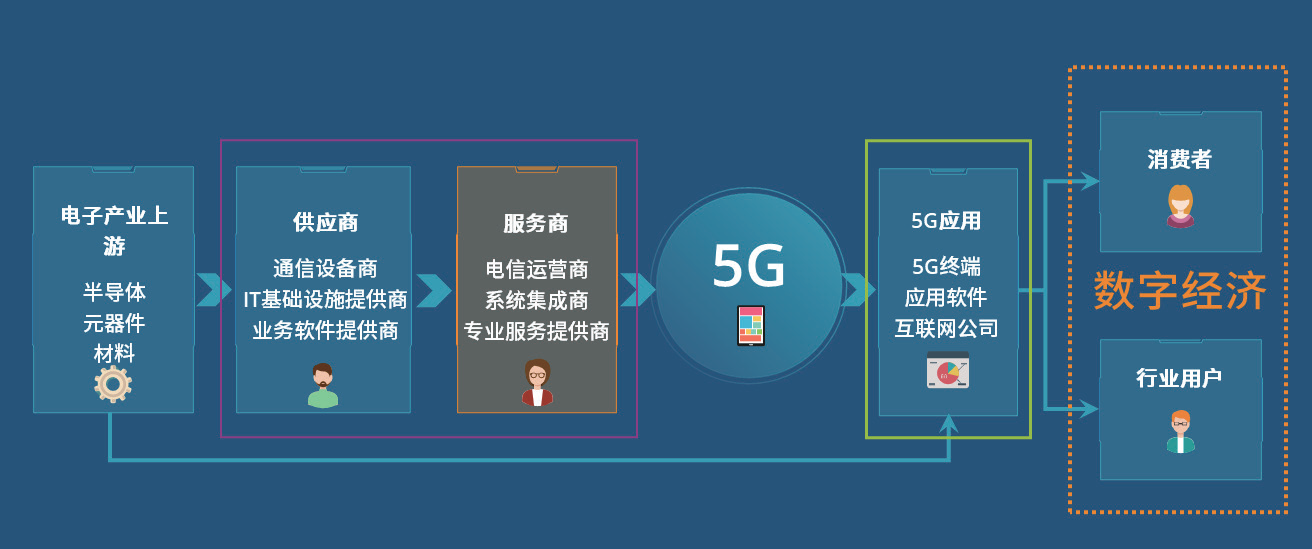

范例運動系統由三個控制器組成,每個控制器通過一個SERCOS適配器連接一個驅動器。SERCOS是連接數字驅動器的工業標準。所有的運動節點都用以太網卡連接到標準的以太網。

調節器內的“運動計劃器”管理每個驅動器的位置信息,以控制點動、移動、和聯動操作。每個驅動器作為一個運動軸,其中一個軸是主軸,其它兩個為從動軸。每個從動軸都與主軸以1:1的比率聯動。連接到主軸的控制器以一定時間間隔向連接到從動軸的控制器發送位置基準。

在系統內所有節點的時鐘是同步的,它使用IEEE1588協議達到以太網的時鐘同步。在底板上的時鐘同步是用先與IEEE1588的專用協議實現的。

系統時鐘同步

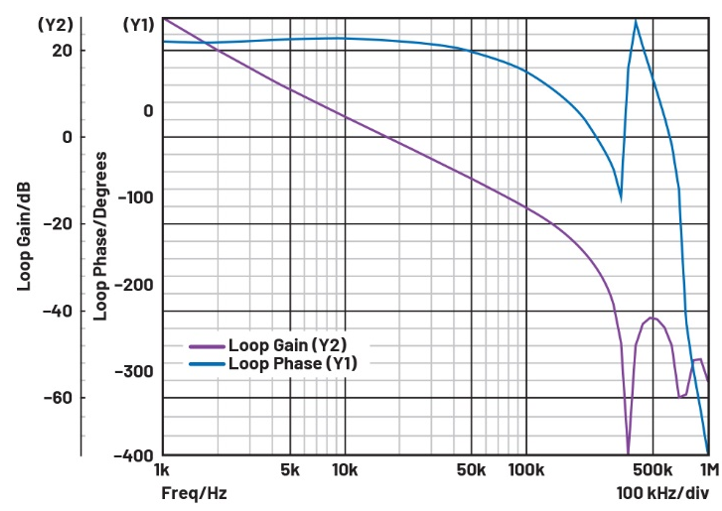

網絡時鐘同步是在以太網適配卡上實現的,這個適配卡包含一個FPGA硬件輔助電路,用于對進入和輸出的IEEE1588協議報文打上時間印記。這個FPGA包含一個64位,每片25納秒的高分辨率的可調諧時鐘。

1588協議運行在一個50MHz PowerPC CPU上,1588代碼和按1588協議的規定的FPGA交互作用使從站的時間與子網上與此相關的主站時鐘同步。調諧算法在每個1588同步刷新周期調節這個FPGA可調諧時鐘的頻率。

這個適配器也包含一個連接底版的接口芯片,底版芯片的時鐘與1588時鐘同步。在這個適配器上的底版接口作為主時鐘,在底版上的其它時鐘都與這個適配器上的主時鐘同步。底版時鐘與1588時鐘的同步使用一個簡單的算法。這個適配器表示一個1588邊界時鐘節點而底版時鐘劃為“外部”時鐘。

運動的同步

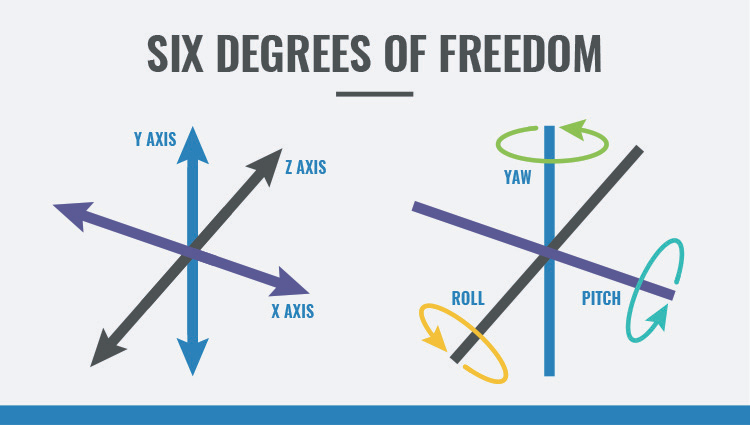

基本的運動控制要求在一個節點的運動任務的運行要與其它所有節點同步。節點之間的所有事務都建立在同步刷新周期基礎上。對控制器與傳動和控制器與控制器之間的兩種事務是相同的。

控制器對驅動的事務:在周期的開始控制器發送插值位置刷新每個驅動器,驅動器使用這個位置刷新值控制電機的閉環位置和速度,每臺驅動器向控制器返回它的實際位置,控制器計算一個新位置并周期重復,這個操作持續一個位置刷新周期。

控制器對控制器的事務:在周期的開始,主軸控制器向每個從動軸發送位置基準,每個從動軸的控制器用這個位置基準計劃本軸的運動。

為了同步整個系統的運動,運動任務和位置的刷新要與1588時鐘同步,FPGA內的一個小電路提供對CPU的周期中斷來觸發這個位置刷新周期。這個電路將一個裝入目標寄存器的時間與當前的1588時鐘時間比較,在當前時間與目標時間符合時產生一個中斷。在這個中斷子程序內,CPU還會裝入一個新的目標時間,它等于當前目標時間加上周期時間,然后重復這個過程。周期時間和相位是在節點配置過程中設置的。

評論