免費的 I/O:改進 FPGA 時鐘分配控制

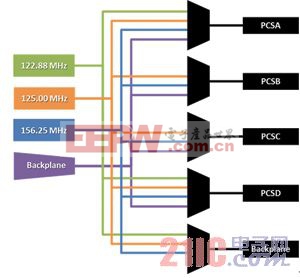

圖1中,FPGA的SERDES/PCS核可以使用幾種可選的連接。PCS quad可用于多種、雙工SERDES通道,連接到各種千兆以太網接口或AMC背板。本文引用地址:http://www.j9360.com/article/162246.htm

● PCSA——來自板上122.88、125或156.25 MHz的時鐘源。但是,如果使用了122.88 MHz,這將禁止PCSA上任何非CPRI接口。PCSA也可以接收來自AMC背板的時鐘。

● PCSB和PCSC——來自板上125或156.25 MHz器件的時鐘源。它們還可以從AMC背板接收時鐘。該時鐘允許不同的速率或相同的速率時鐘分別提供給PCSB和PCSC參考時鐘。

● PCSD——來自板上122.88、125或156.25 MHz器件的時鐘源。它們還可以從AMC背板接收時鐘信號。

● 背板——連接AMC edge-finger (TCLKB)的遠程通信時鐘。這個時鐘可以在不使用時禁用。

* 來自AMC的時鐘:這個時鐘能夠為所有4個quad提供PCS參考時鐘的驅動參考時鐘源。

* 輸入AMC的時鐘:這個時鐘能夠驅動AMC模塊到背板,并且可以是任意PCS quad的同一個參考時鐘源。

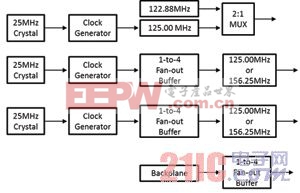

如圖2所示,AMC時鐘網絡最初通過多個時鐘發生器控制,14個扇出緩沖器和一個2:1多路開關。該方案需要38個I/O來進行時鐘分配控制,還需要占用大量電路板面積。

圖2 傳統AMC時鐘網絡機制

利用一個可編程的時鐘管理器件,可以大大地優化網絡(如圖3所示)。該方案僅需要18個I/O來進行時鐘分配控制,節省了20個I/O可用于其他功能。此外,使用這種設計節省了超過3平方英寸的電路板面積。

這些方案通過使用兩個可編程時鐘管理器件來控制(見圖4)。有幾個板上振蕩器可以合成和/或扇出作為幾個時鐘的輸入。所有的時鐘變量都可以通過對時鐘管理器件的編程來進行管理。

圖3 優化的AMC時鐘網絡設計

評論