賽靈思System Generator中的時間參數

基于模型的設計(MBD)因其在縮小實時系統抽象的數學建模和物理實現之間差距方面的光明前景而備受關注。通過使用相同的源代碼進行算法分析、架構探討、行為模擬和硬/軟件設計,MBD有望縮短系統設計周期。

本文引用地址:http://www.j9360.com/article/161393.htm無需通曉硬件描述語言(HDL),為DSP提供的Xilinx System Generator即可讓控制工程師在熟悉的Simulink環境中設計系統,然后在FPGA中實施。為此,必須將受控系統(通常稱之為設備)的數學模型參數值(如連續/離散時間傳遞函數或狀態空間描述)與FPGA系統時鐘頻率和數字控制器的采樣率關聯起來。

FPGA中的數字控制器

之前,在實施FPGA時,控制器設計人員在首次驗證控制策略和參數并進行控制器和設備模型的高級模擬(如使用Simulink)后,可能還會使用一種低級的HDL。HDL控制器設計與Simulink模擬之間的對應性將由HDL測試平臺加以驗證。為在閉環系統中驗證控制器設計,該測試平臺必須包括設備模型。對于缺乏HDL和FPGA技術專業背景的設計人員及大多數控制工程師而言,要實現上述這一切卻并非易事。在這種情況下,如Xilinx System Generator之類的高級建模和設計環境正是理想之選。

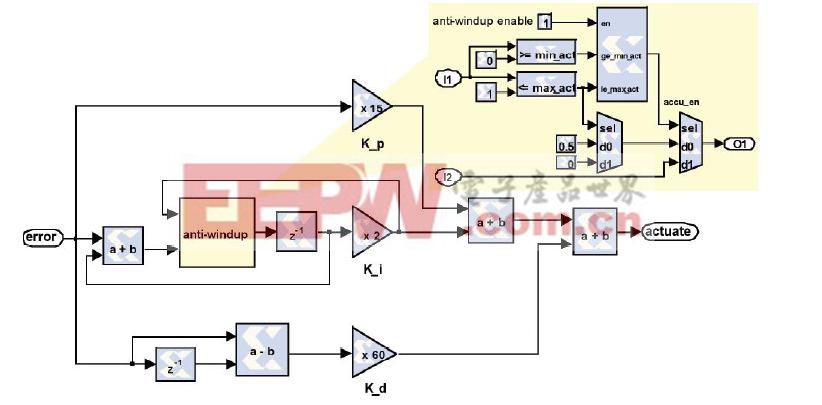

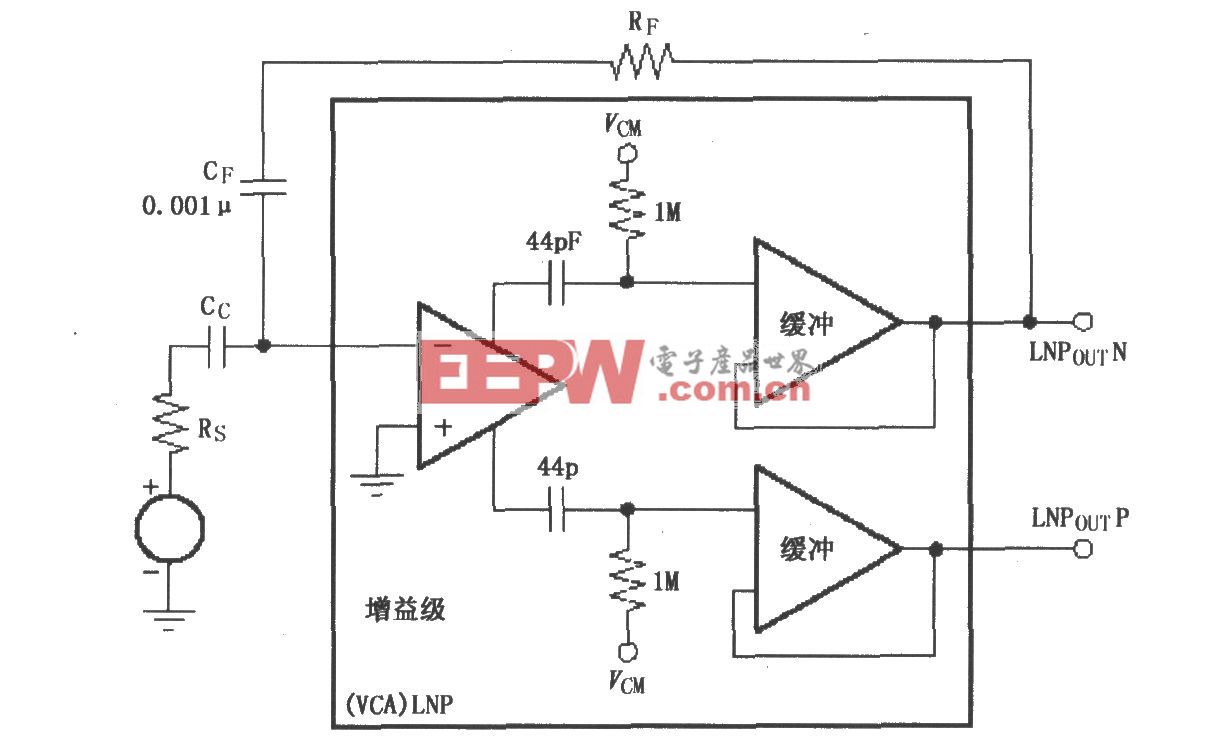

鑒于許多控制器仍基于傳統的比例-積分-微分(PID)結構,借用一個PID控制器來演示本文的觀點。同時,本文概述的方法也可較好地處理超前滯后補償器、狀態空間觀測器或者自適應控制器等其他常用的控制組件。圖1所示為采用源自賽靈思模塊集的模塊而設計的PID控制器。

圖1 基于System Generator模塊且支持抗飽和功能的PID控制器

這里沒有使用賽靈思的累加器模塊,而是采用基本的加法器和寄存器構建塊來實現集成。這樣做可以插入如圖1所示的抗飽和邏輯,以便在控制器輸出的積分部分達到執行器規定的飽和限值時,凍結累加器寄存器中的內容。抗飽和邏輯可使PID控制器成為非線性系統,并對系統的總體動態產生積極的影響。

圖2所示的模塊參數菜單可用來配置各種信號的控制參數和字寬。

圖2 PID控制器的定制參數菜單

另外,設計人員還能在此啟用或停用抗飽和函數。利用該菜單,無需修改低級HDL代碼即可方便地進行實驗。

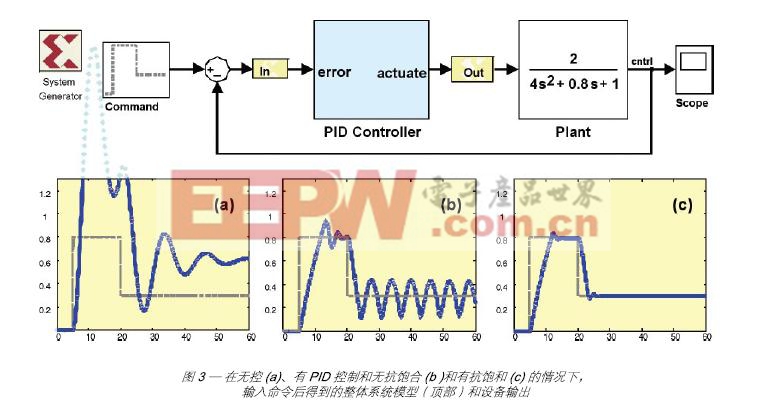

圖3所示為整體系統模型,其不僅包含控制器,還有基于標準Simulink模塊的設備和模擬測試平臺。借助該模型,設計人員可采用連續或離散時間傳遞函數進行設備建模,而在HDL測試平臺中則只能使用離散時間函數。值得一提的是,采用System Generator方法,就可以通過同一個高級模型完成從系統建模、模擬、驗證直至實施的任何工作。

評論