基于DDS的高速定時同步方法

摘要:定時同步是高速數據傳輸的關鍵技術也是難點問題。在對鎖相環數字化設計、DDS原理結構和參數設計進行研究的基礎上,提出了一種基于DDS的高速定時同步方法,對該定時同步方法的原理結構框圖進行了詳細的論述,對具體參數進行了設計。采用這種定時同步方法的高速解調器進行了原理實驗測試,取得了滿意的結果,所提出的定時同步方法對高速數據傳輸方案設計提供了參考。

關鍵詞:定時同步;鎖相環;高速傳輸;DDS

0 引言

在數字通信系統中,定時同步是接收機必須完成的一個重要工作,定時同步的好壞直接影響到數字接收機的性能。高速數據傳輸對定時同步提出了新要求,同步算法結構必須簡單有效以降低器件速度限制。

定時同步通常采用3種基本方式實現:模擬方式、數字方式和混合方式。鑒于模擬電路所固有的穩定性差、一致性差等問題,模擬方式目前已經很少使用。數字方式采用一個獨立于發送端的時鐘對接收信號進行直接采樣,然后通過插值運算得到信號在最佳判決時刻的近似值。數字方式對采樣率要求較高,通常要求采樣率是符號速率4倍以上,對ADC有較高的要求。混合方式通過提取接收信號中的時鐘誤差信息來調整ADC采樣時鐘,實現定時同步時鐘恢復。混合方式具備數字方式結構可靠、成本低、處理靈活等優點,同時降低了對ADC的要求,采樣率只需要2倍符號速率,是高速定時同步的較好選擇。

所提出的高速定時同步方法采用了混合方式。ADC的采樣時鐘由DDS產生,DDS相當于鎖相環中的VCO。鎖相環的鑒相器、環路濾波是全數字的,在FPGA內實現。定時同步是通過鎖相環閉環調整實現的。

1 定時同步數字鎖相環路設計

定時同步環路采用理想二階鎖相環。鎖相環由鑒相器、環路濾波器、壓控振蕩器(VCO)組成。理想二階環的鑒相器增益表示為Kd。環路濾波器傳遞函數為:

F(s)=K1+K2/s (1)

式中:K1為環路濾波器比例通路的增益系數;K2為環路濾波器積分通路的增益系數。

壓控振蕩器的傳遞函數為:

V(s)=Ko/s (2)

式中Ko為VCO的增益。

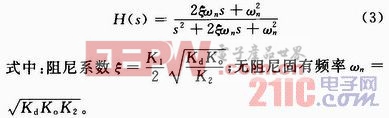

由式(1),式(2)可得到理想二階環的傳遞函數:

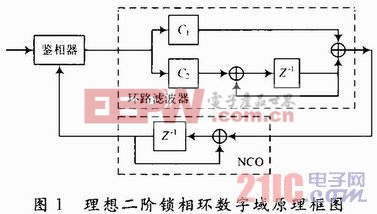

根據脈沖響應不變法,由式(3)可得到理想二階鎖相環的數字域原理框圖如圖1所示。

圖1中環路濾波器的兩個參數C1,C2計算式為:

式中:ts為采樣周期。

阻尼系數為固定值通常取ζ=0.707,無阻尼固有頻率ωn的取值根據鎖相環頻率捕獲范圍確定,可取為與要求捕獲頻率相近的值。由式(4)計算出C1和C2即完成理想二階數字鎖相環的參數設計。

評論