一種基于FPGA的DDR SDRAM控制器的設計

2.2 CMD命令模塊

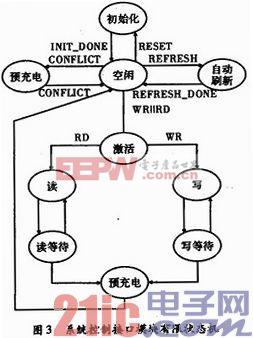

CMD命令模塊ddr_command由仲裁模塊以及命令產生模塊構成。仲裁模塊的作用主要是仲裁初始化請求、刷新請求以及讀寫請求的優先級,并產生初始化響應initial hold、刷新響應refresh hold和讀寫響應sdram wr hold。命令產生模塊則是實現存儲器與控制之間的命令通信,直接產生存儲器所需的CKE、CS_N,RAS_N,CAS_N,WE_N等命令信號。除此之外Read/Write所需的行列地址和簇地址也由命令模塊產生。命令產生模塊接收到來自CMD命令解析模塊的操作命令后,根據數據選通倍號OE對數據通路模塊進行有效控制:OE為1時,進行Write操作;OE為0時,進行Read操作。

2.3 數據通路模塊

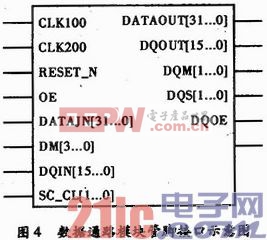

數據通路模塊ddr_data_path受命令產生模塊的OE信號控制,其管腳接口如圖4所示。OE為1時,數據可由DQIN引腳寫入DDR SDRAM;OE為0時,數據可從DDR SDRAM的DQIN引腳讀出。

由于DDR SDRAM在時鐘的上升沿和下降沿能均觸發數據,使得用戶端的數據寬度是DDR SDRAM的兩倍。進行Read操作時,DQ pins上的雙倍速率數據經過邊沿觸發器,在DQS信號的兩個邊沿同時采樣數據,然后這些數據會通過另一套可配置的寄存器被傳送到系統的時鐘域。進行Write操作時,用戶端寄存器輸出的數據會被傳送到控制器的寄存器中,進而被存放到DQ pins上。數據通路模塊在與存儲器的接口處完成了兩個轉換:一是翻倍來自存儲器的數據總線寬度;二是以400 MHz的時鐘頻率接收存儲器在時鐘上升和下降沿發出的數據。

電容器相關文章:電容器原理

fpga相關文章:fpga是什么

電荷放大器相關文章:電荷放大器原理 漏電開關相關文章:漏電開關原理 鎖相環相關文章:鎖相環原理

評論