基于FPGA的頻率特性測試儀的設計

摘要:為設計一款便攜式頻率特性測試儀,該系統以大規模可縭程邏輯器件為實現載體,采用了基于FPGA體系結構的集成化設計方案,以VHDL為設計語言,設計了包含掃頻信號源、測幅、測相及顯示等電路,系統經峰值檢測和相位檢測分別完成了被測網絡的幅頻和相頻特性測量及曲線顯示,經調試功能上能滿足大部分系統要求,對RC串并聯電路進行測量誤差為0.4%;該系統具有探作簡單、成本低廉、性能穩定等特點,具有較強的實用價值與發展前景。

關鍵詞:頻率特性;現場可編程門陣列;直接數字頻率合成DDS;正弦信號

在電子測量中,經常需要對電路網絡的阻抗特性和傳輸特性進行測量,其中傳輸特性包括增益和衰減特性、幅頻特性、相頻特性等。用來測量這些特性的儀器稱為頻率特性測試儀,簡稱掃頻儀。目前市場上頻率特性測試儀有模擬式和數字式兩種,它們都存在體積大、價格貴、操作復雜的缺點,在實際應用中用戶很難接受。本文采用了現場可編程門陣列(FPGA)及外圍測量電路設計了一種簡易便攜式的頻率特性測試儀,其性能上能滿足大部分系統要求的頻率響應特性的測量,具有較高的實用價值。

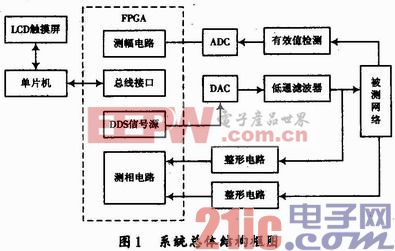

1 系統總體設計

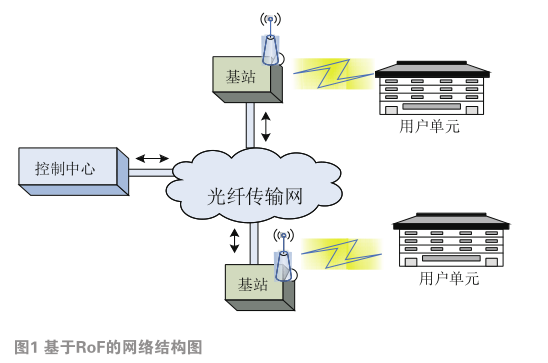

本系統以FPGA以核心,由掃頻信號源、測幅電路、測相電路、有效值檢測、整形電路、LCD觸摸屏等模塊構成。系統總體結構框圖如圖1所示。系統工作時,由掃頻信號源輸出頻率可步進的正弦信號作為被測網絡的輸入信號,信號經過被測網絡一路送到有效值檢測電路中進行幅值檢測,該幅度值與與掃頻信號源輸出信號的幅值進行比較,得到該點的幅頻響應;另一路信號送到整形電路限幅整形后送至FPGA內部的測相電路進行相位差的測量,將相位差與信號的整個周期進行比較,就可以得到該點的相頻響應。

2 系統主要模塊設計

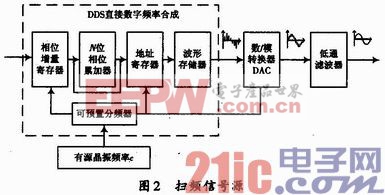

2.1 掃頻信號源的設計

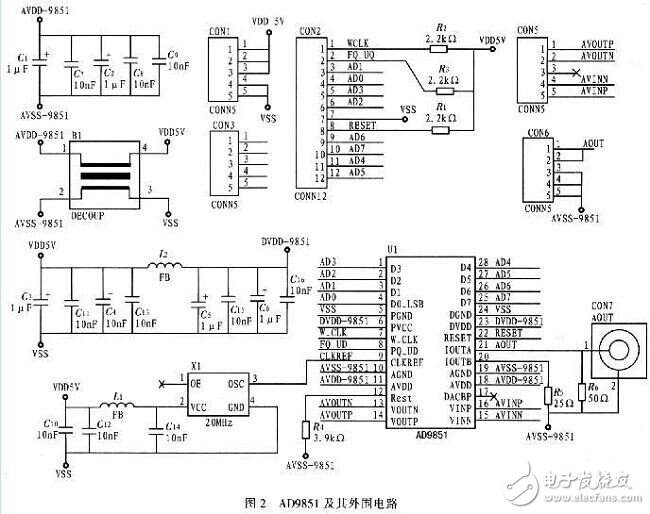

直接數字式頻率合成DDS具有相對帶寬高,頻率轉換時間短,頻率分辨率高,及輸出相位連續,頻率、相位和幅度均可實現程控的優點,掃頻信號源選擇采用DDS信號源。實現過程如圖2所示,將待產生的正弦波數據存入波形存儲器中,在時鐘信號fclk的控制下,通過由頻率控制字M控制的相位累加器輸出相位碼,將存儲于波形存儲器中的波形量化采樣數據值讀出,經D/A轉換成模擬信號,再經低通濾波器濾去除D/A轉換帶來的小臺階和數字電路產生毛刺,獲得高精度、高純度的正弦信號。

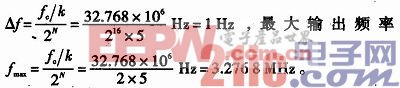

輸出信號的頻率可由公式:fout=(fc/k)/2N×M計算得到,通過改變分頻比k及相位累加器步長M可以改變出信號的頻率。本設計中取fc=32.768 MHz,分頻比k=5,相位累加位數N=16.則頻率步進最小值為:

考慮到DDS的輸出存在雜散噪聲,信號源最大輸出頻率選定為1 MHz。

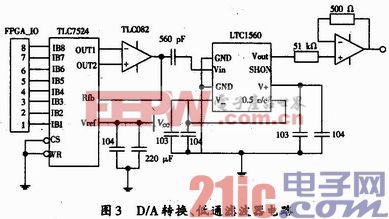

數模轉換采用TI公司的8位D/A芯片,其轉換周期為100 ns;LPF低通濾波器采用凌特公司的1 MHz/500 kHz五階連續時間低噪聲低通橢圓濾器LTC1560-1,電路連接使其工作在截止頻率為1 MHz。電路如圖3所示。

2.2 幅頻特性測量模塊

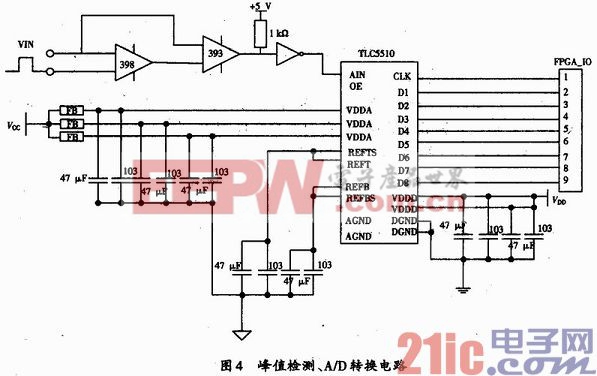

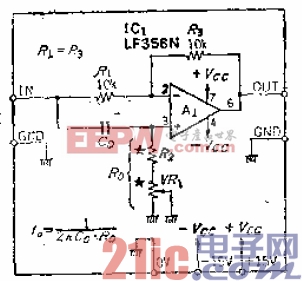

該模塊首先對被測網絡的輸出信號進行峰值檢測,檢測出來的峰值經A/D轉換器量化成數字信號,送入到FPGA內部的測幅電路中完成處理運算得到網絡的幅頻特性。峰值檢測選用LF398構成采樣-保持電路,對輸入和輸出信號進行采樣,篩選出峰值并予以保持。A/D轉換選用TI公司生產的8位閃速結構數模轉換器TLC5510,它采用CMOS工藝制造,可提供最小20 MS/s的采樣率。峰值檢測及A/D轉換電圖如圖4所示。

模擬信號相關文章:什么是模擬信號

fpga相關文章:fpga是什么

低通濾波器相關文章:低通濾波器原理

鎖相環相關文章:鎖相環原理 網線測試儀相關文章:網線測試儀原理

評論