認清CPLD和FPGA

CPLD和FPGA都是我們經常會用到的器件。有的說有配置芯片的是FPGA,沒有的是CPLD;有的說邏輯資源多的是FPGA,少的是CPLD;有的直接就不做區分,把他們都叫做FPGA。那么兩者到底有什么區別呢?下面我們就以Altera公司的CPLD和FPGA為例來說說兩者的區別。

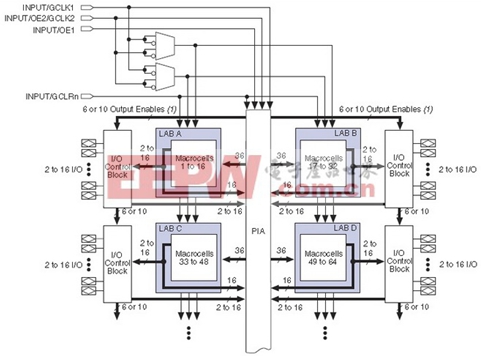

本文引用地址:http://www.j9360.com/article/159017.htm首先我們看一下CPLD的芯片結構,搞清楚CPLD是由哪幾部分組成的。下圖是MAX系列CPLD的芯片結構圖:

從圖中可以清楚的看出來CPLD主要由三部分組成:Macro cell(宏單元),PIA(可編程連線),和IO Control Block(IO控制塊)。每個宏單元都與GCLK(全局時鐘)OE(輸出使能)GCLR(清零)等控制信號直接相連,并且延時相同。各宏單元之間也由固定長度的金屬線互連,這樣保證邏輯電路的延時固定。其中宏單元模塊是CPLD的邏輯功能實現單元,是器件的基本單元,我們設計的邏輯電路就是由宏單元具體實現的。下面我們再來看看宏單元的具體結構:

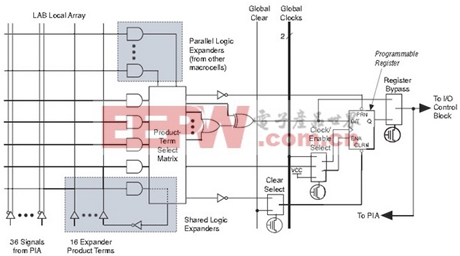

一個宏單元主要包括了LAB Local Array(邏輯陣列),Product-Term Select Matrix(乘積項選擇矩陣)和一個可編程D觸發器組成。其中邏輯陣列的每一個交叉點都可以通過編程實現導通從而實現與邏輯,乘積項選擇矩陣可實現或邏輯。這兩部分協同工作,就可以實現一個完整的組合邏輯。輸出可以選擇通過D觸發器,也可以對觸發器進行旁路。通過這個結構可以發現,CPLD非常適合實現組合邏輯,再配合后面的觸發器也能夠實現一定的時序邏輯。

fpga相關文章:fpga是什么

評論