基于單載波調制器中TS流傳輸的設計和實現

【摘 要】 本文介紹了數字電視地面傳輸廣播中TS流在單載波(ATSC)調制器中的傳輸,詳細說明了ASI接口的轉化,論述了TS流速率與調制器凈數據率的速率匹配問題,并使用CY7B933、CY7C433和FPGA實現了TS流在調制器中的正常傳輸,最終給出了硬件設計結果。

【關鍵詞】ATSC; TS; ASI; SPI; 插空包

1 概述

隨著數字技術的不斷發(fā)展,數字電視取代模擬電視已經是必然的趨勢。當今世界地面數字電視傳輸標準主要有美國的ATSC標準,歐洲的DVB-T標準和日本的ISBT-T標準。ATSC標準是基于單載波調制的技術,它具有傳輸容量大、工作門限低、相同覆蓋條件下要求發(fā)射功率低、抗脈沖干擾能力強、對調諧器要求低等優(yōu)點,同時經過大量的測試已經成功應用于實際的數字電視地面廣播傳輸中【1】。由于編碼器以傳輸流(TS)的形式并配以ASI或SPI接口傳輸到調制器,因此在設計調制器時應該首先考慮接口規(guī)范的不同和速率匹配等問題,本文主要是基于ATSC調制器來討論TS的傳輸。

2 TS流在調制器中的傳輸

2.1 調制器結構

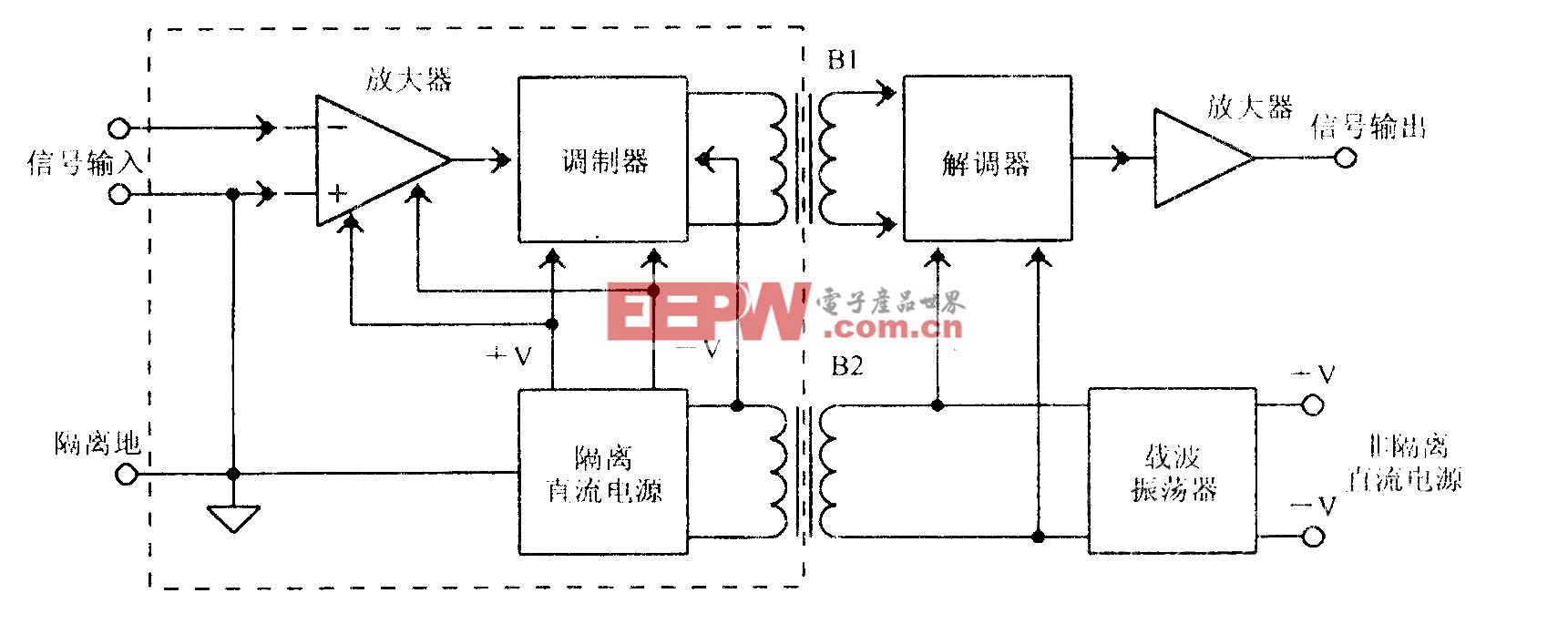

圖一 調制器中的TS流傳輸

在無線廣播數字電視傳輸系統(tǒng)中,統(tǒng)一規(guī)定以MPEG-2的傳輸流即TS流(transport stream)形式進行傳輸,也就是說視音頻信息經過編碼器的處理形成TS流的標準形式,每個TS包有188個連續(xù)的字節(jié),其中位于包頭的第一個字節(jié)固定為47H。編碼器輸出接口一般分為兩種形式,ASI口(Asynchronous serial interface)和SPI口(Serial Peripheral Interface),前者是一種高速串行數據通訊接口,具有高速、可靠、準確等特性;后者屬于一種并行總線接口,易于進行數據處理。但無論采用哪種接口,調制器都需要對其進行速率匹配的處理,因為雖然編碼器的輸出速率可以固定在4Mbps到20Mbps不等,但實際傳送的每個TS包的速率不固定,且TS包之間的間隔也不固定,這對于需要連續(xù)處理數據的調制器來說是不允許的。所以設計的調制器可傳送的凈數據率必須大于編碼器的輸出速率,并在TS流中適當的插一些空包(符合MPEG-2標準),以獲得連續(xù)的碼流。

圖一表示了TS流在調制器中的傳輸過程,其中片內FIFO即用于上訴的速率匹配,接下來TS流需要經過擾碼,外編碼和交織等模塊最后組幀輸出用于調制,中間的交織器由于使用RAM,可以間接起到由于組幀時插入同步信息的數據緩沖作用,同時組幀輸出的數據使能反饋回FIFO要新的TS流,周而復始。本文設計的這種調制器結構具有修改性強的特點,原因在于一旦幀場結構有所變化,只需要修改相應的數據使能的產生,而與前級處理無關,有利于TS流在調制器中的連續(xù)傳輸。

2.2 TS流傳輸中ASI口的轉化

圖二 ASI口轉化的實現框圖

ASI是一種固定波特率的異步串行接口,其突出特點是:速度快,固定波特率,準確。來自不同數據信源的波特率可能是不同的,通過在這些數據中間插入同步字而使用固定波特率(270M)傳輸【2】。此外,其數據還經過8Bit到10Bit編碼,在傳輸數據的空余段插入同步字,具有較強的抗擾、錯誤檢測和再同步能力。

為了得到并行傳輸的TS流數據,需要對ASI口進行轉化,如上圖所示,CYPRESS公司的CY7B933和CY7C433配合使用,可以很好的解決這個問題,他們的主要引腳如下:

CKR:CY7B933的恢復時鐘,一般為27M,配合數據的輸出;

RDY:數據輸出準備,低有效,表示數據已經被接收準備傳送,屬于正常;

SC/D:特殊字符/數據選擇,低有效,表示Q0~7為有效數據;

Q0~7:CY7B933并行數據輸出;

Read_ena:FIFO的讀使能信號,低有效;

Write_ena:FIFO的寫使能信號,低有效;

HF:FIFO的半滿信號,低有效;

可將RDY信號和SC/D信號組合產生FIFO的寫信號,將有效的數據寫入FIFO,FPGA通過判斷半滿信號HF連續(xù)地從FIFO中讀取一個TS包長度的數據。但只得到TS數據流是不夠的,必須加入一些指示線證明數據的正確性,相似于SPI口的標準形式,產生sync用于指示包頭位置,valid用于指示一個數據包的有效性,并配合FPGA本地的時鐘clk(一般30M),方便后級處理。搜索包頭的流程圖如下:

圖三 搜索TS流包頭流程圖

2.3

2.3

TS流傳輸中插空包處理

經過接口處理的TS流雖然包括sync和valid的信號,但是速率仍然和調制器的其他模塊有沖突,尤其數據流的連續(xù)性由組幀時的使能控制,所以仍然必須對TS流進行插空包的處理,且使輸出符合幀結構特點,這也是本文設計調制器的關鍵。

這里又得需要一個FIFO,但由于編碼器輸出速率和調制器凈數據率往往相差不大,可以考慮使用片內FIFO,在對FIFO輸出的數據進行判斷時,需要用到sync指示線,為了方便處理,將FIFO設為9位位寬(sync、data),深度設為4K。相似于上述的ASI轉化,讀FIFO時也需要判斷半滿信號HF,不同的是要確保寫入FIFO的第一個數據是包頭47H,這樣可以保證以后每次讀取一個完整的TS包。當HF無效時插入空包,空包的具體格式為:

圖四 空包數據結構

但是值得注意的是由于ATSC標準中的幀長不一定是TS包的整數倍,也就是說讀FIFO或插空包時可能不會是一個完整的包,為此需要新增狀態(tài)機FIFO_stop,記錄停止的位置(保持188計數器的值),以便使能再次有效的時候繼續(xù)處理上回的數據,具體狀態(tài)機的實現如下圖所示:

圖五 插空包的狀態(tài)機實現

3.硬件實驗結果

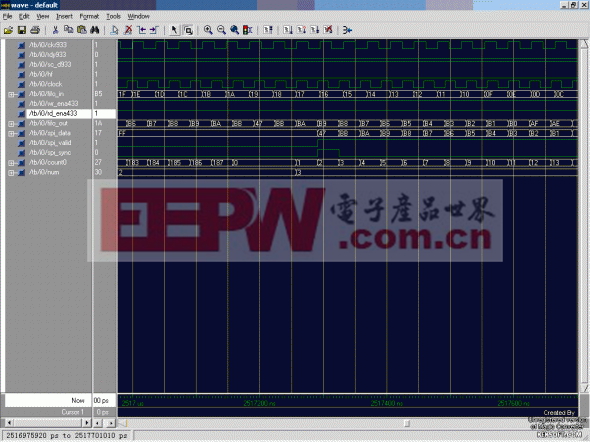

(見TIF圖像附件)圖六:ASI轉化仿真示意圖

(見TIF圖像附件)圖七 插空包過程的仿真示意圖

本文的硬件設計采用ATERA公司的APEX系列芯片【3】,仿真工具為MENTOR公司的ModelSim軟件,經過仿真和硬件調試,工作正常。

圖六所示的仿真結果中采用片內FIFO模仿CY7C433,而且經過硬件調試,ASI轉換模塊良好,搜索包頭47H迅速,達到系統(tǒng)的速率要求。插空包模塊的仿真波形(圖七)更加準確的解釋了狀態(tài)機之間的跳轉,其中state的數值表示如下:

0:系統(tǒng)復位;1:讀FIFO工作;2:插入空包;3:讀FIFO或插空包暫停。

可見系統(tǒng)起始狀態(tài)FIFO未達到半滿所以插入了2個空包,其后開始讀FIFO,由于讀到一半,幀使能信號gen_ena_bit為低,進入狀態(tài)3,待使能信號再次為高,接著上回的位置繼續(xù)讀取FIFO,位置計數器rd_cnt開始計數。

4.結束語

本文設計的調制器TS流傳輸方案,利用CYPRESS公司的CY7B933和CY7C433的配合,通過FPGA作為邏輯控制,解決了TS流傳輸中的接口不統(tǒng)一和速率不匹配等問題,并通過了硬件的仿真和調試,可應用于許多現有的數字電視地面廣播傳輸系統(tǒng)中,如美國的ATSC標準和中國的ADTB_T,具有很強的實用性。而且就ASI轉化部分而言也可以應用于以DVB_T為代表的多載波傳輸系統(tǒng),有一定的通用性。

參考文獻

【1】 The Grand, “The U.S. HDTV standard,” IEEE Spectrum, April, 1995, pp. 36-45.

【2】 關東亮,余松煜. 一種新的高速ASI的設計與實現. 數據采集與處理, 2001(12):490-493.

【3】 夏宇聞. 從算法設計到硬線邏輯的實現. 北京:高等教育出版社,2001. 122-159.

評論