基于PEX8111的CompactPCI Express 混合橋接板設計

2.3 時鐘設計

發送器以2.5 Gb/s的速率定時輸出數據。實現該速率的時鐘必須精確在中心頻率±300 ppm內,它最大允許每1 666個時鐘偏離1個時鐘。設備獲取時鐘輸入的方式有兩種:采用本板時鐘和使用外部輸入時鐘,該設計使用外部時鐘。如果使用擴展頻譜定時(Spread Spectrum Clocking,SSC)功能,一般都要求鏈路上的發送器和接收器必須使用同一參考時鐘,SSC是一種用于緩慢調制時鐘頻率的技術,以便降低時鐘中心頻率處的EMI輻射噪音。有了SSC,輻射的能量就不會產生2.5 GHz的噪音尖峰信號,因為輻射能量被分散到2.5 GHz周圍小的頻率范圍。

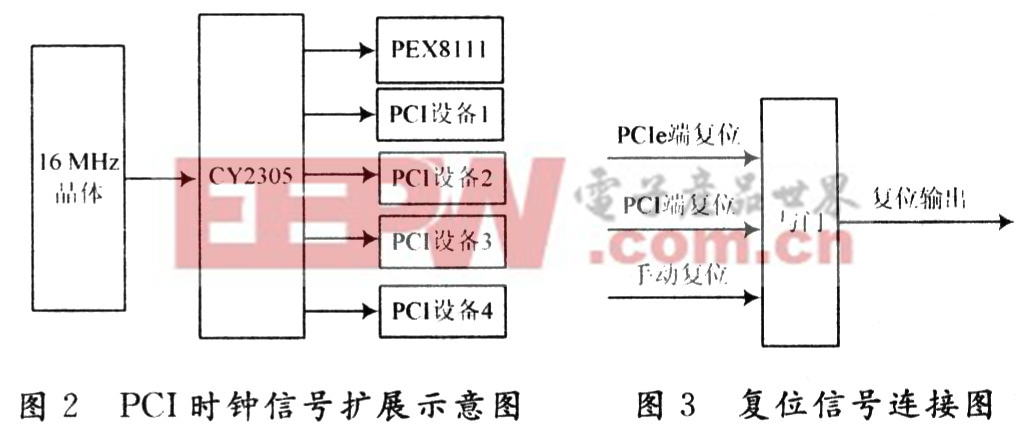

本模塊需要為外接的PCI設備提供時鐘信號,如圖2所示。33 MHz晶體作為時鐘源,通過零延時緩沖器CY2305輸出5路時鐘,并分別作為PEX8111和4個外接PCI設備的時鐘源。零延時緩沖器是一種可以將一個時鐘信號扇出多個時鐘信號,并使這些輸出之間有零延時和很低偏斜的器件,所以可以認為4個外接PCI設備工作在同一時鐘下。本文引用地址:http://www.j9360.com/article/157759.htm

2.4 PCI接口設計

該PCI接口實現的功能為PCI的HOST功能,包含總線信號和仲裁信號。在進行該模塊設計時需要注意連接器J1的信號定義與標準的J1接口有一些差別。因為如果將PCI總線信號完整的引出需要兩個連接器J1,J2配合使用,但是因為高速連接器XSJ3處于原本J2的位置上,因此在缺少部分信號針的情況下無法實現完整PCI host功能,采取使用了特殊的CPCIJ1連接器的方法解決這個問題,這種連接器比普通J1連接器多出15個信號引腳,可以使用這些多余的引腳引出REQn,ACKn信號。

2.5 電源設計

PEX8111芯片需要用到3種電源。其中PCI總線信號為5 V,I/O供電電壓為3.3 V,串行收發器的電源電壓為1.5 V,所以本模塊需要提供5 V,3.3 V和1.5 V三種電壓源。

5 V.3.3 V電壓由系統提供,1.5 V由3.3 V電壓轉換獲得,選取國家半導體公司的LP2992作為3.3~1.5 V電壓轉換模塊。該模塊具有90%以上的轉換效率、簡單的外圍電路、更小的封裝、2.5%以下的紋波電壓等特點。

2.6 復位設計

復位輸入有三個,來自PCIe端的復位,來自PEX8111復位輸出,手動復位信號,保證在主機側出現冷復位和要求本板單獨復位的情況下,可以將復位信號向下傳遞,如圖3所示。

3 高速電路設計

基于CPCIe總線的電路屬于高速電路,在電路設計之初就采用仿真工具進行驗證,并根據仿真結果不斷調整自己的設計。

對所設計的電路進行仿真是該設計的關鍵點。PEX8111芯片信號的種類和數目都比較少,在芯片外圍沒有復雜的邏輯設計,在電路設計上對時鐘和電源的要求也比較簡單,但是對傳輸在PCB上高速差分信號的質量有很高的要求,這個要求也是當前所有高速設計面臨的共性問題。由于高速PCB設計需要考慮的因素很多,比如介質、平面分割、信號的等長等,傳統的設計準則已經不再準確,所以需要依靠仿真工具來提供設計依據。在該設計中采用的仿真工具是Mentor公司Hyperlynx GHz,Hspice仿真模型,由器件的生產廠家提供。

仿真的過程主要包括前仿真和后仿真,以下敘述兩種仿真的具體內容。

評論