利用串行RapidIO實現FPGA協處理

同時,開發人員不但要跟上日益提高的性能需求,還得注意保持成本低廉 有效利用基于串行RapidIO的FPGA作為DSP協處理器就能達到這些目的

有效利用基于串行RapidIO的FPGA作為DSP協處理器就能達到這些目的

由于三重播放應用集合了話音、視頻和數據應用,因此必須采用新算法來設定其開發和系統優化策略的參數 其間,開發人員要解決以下問題:構造可調整可擴展的架構、支持分布式處理、采用基于標準的設計,以及針對性能和成本進行優化

其間,開發人員要解決以下問題:構造可調整可擴展的架構、支持分布式處理、采用基于標準的設計,以及針對性能和成本進行優化

仔細研究一下就會發現,為滿足應用需求而要、面對的這些挑戰主要涉及兩個主題:一是連接性,從本質上說就是實現不同設備、板卡和系統之間的“快速”數據轉移;二是計算能力,指設備、板卡和系統中分別可用的處理資源

運算平臺之間的連接

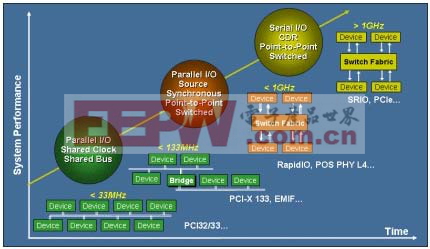

基于標準的設計通常比“自由發揮”的設計簡單得多,也是今天的典型設計模式 并行連接標準(PCI、PCI-X、EMIF等)雖能滿足當前需求,但若考慮到可調整性和可擴展性就有所不足了

并行連接標準(PCI、PCI-X、EMIF等)雖能滿足當前需求,但若考慮到可調整性和可擴展性就有所不足了 隨著分組處理技術的不斷進步,連接標準的發展趨勢顯然傾向于高速串行連接

隨著分組處理技術的不斷進步,連接標準的發展趨勢顯然傾向于高速串行連接 從圖1中就能看出這一趨勢

從圖1中就能看出這一趨勢

諸如PCIe和GbE/XAUI之類的高速串行標準在臺式機和網絡行業已有應用 但無線通信設施中的數據處理系統對互連方面的要求又稍有不同,它要求:

但無線通信設施中的數據處理系統對互連方面的要求又稍有不同,它要求:

1. 管腳數少;

2. 需進行底板以及芯片到芯片的連接;

3. 帶寬和速度可調;

4. 具備DMA和消息傳遞功能;

5. 支持復雜可調整的拓撲;

6. 支持多點傳送;

7. 高度可靠;

8. 支持當日時間(time of day)同步;

9. 可提供服務質量(QoS)

圖1:向串行連接的發展趨勢

串行RapidIO (SRIO)協議標準可輕松滿足以上大部分要求,甚至超出這些要求的標準 因此,串行RapidIO已成為無線通信基礎設備中用于數據層(data plane)互連的主流連接技術

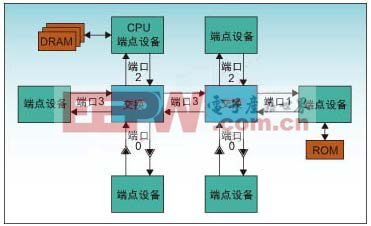

因此,串行RapidIO已成為無線通信基礎設備中用于數據層(data plane)互連的主流連接技術 SRIO網絡建立在兩個“基本模塊”基礎之上:端點設備(Endpoint)和交換設備(Switch)

SRIO網絡建立在兩個“基本模塊”基礎之上:端點設備(Endpoint)和交換設備(Switch) 端點設備負責收發數據包,交換設備負責在端口之間傳遞數據包,但不負責數據包的解釋

端點設備負責收發數據包,交換設備負責在端口之間傳遞數據包,但不負責數據包的解釋 圖2給出了SRIO網絡的構建模塊

圖2給出了SRIO網絡的構建模塊

圖2:SRIO網絡的構建模塊

按規范定義,串行RapidIO有用3層架構,如圖3所示

圖3:SRIO架構

其中包含:

物理層――負責描述器件級接口規范,例如分組傳輸機制、流量控制、電特性以及低級錯誤管理

評論