基于IXP2400的安全網關實現研究

摘要: 討論了在IXP2400上應用IPSec實現安全網關的一種方案,可為通過的業務流提供較強的安全性。

關鍵詞: 網絡處理器; IXP2400; 微引擎; IPSec

IPSec是一種基于IP層的通信安全機制,是目前唯一一種可為任何形式的通信提供安全保障的協議,因而實現具有IPSec功能的網關能保證IP層通信的安全。然而,用IPSec對數據包進行認證、加/解密處理等,都是比較耗費資源的工作,容易使具有IPSec功能的網關設備出現瓶頸問題;同時,基于ASIC研發具有這類復雜功能的新產品更為困難。因此,傳統的網絡解決方案已在處理速度和靈活性兩方面受到挑戰。具有通用CPU的靈活性和ASIC芯片的執行速度的可編程網絡處理器的出現,為IPSec機制在線速網關設備的應用提供了新途徑。

本文介紹了Intel的IXP2400網絡處理器的特點、結構以及IPSec體系結構,討論了在IXP2400中以IPSec實現安全網關的一種方案。

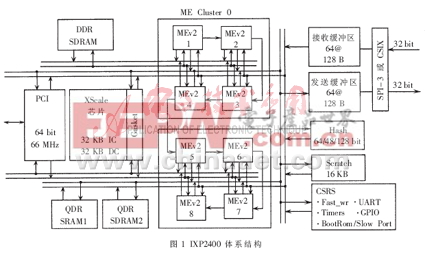

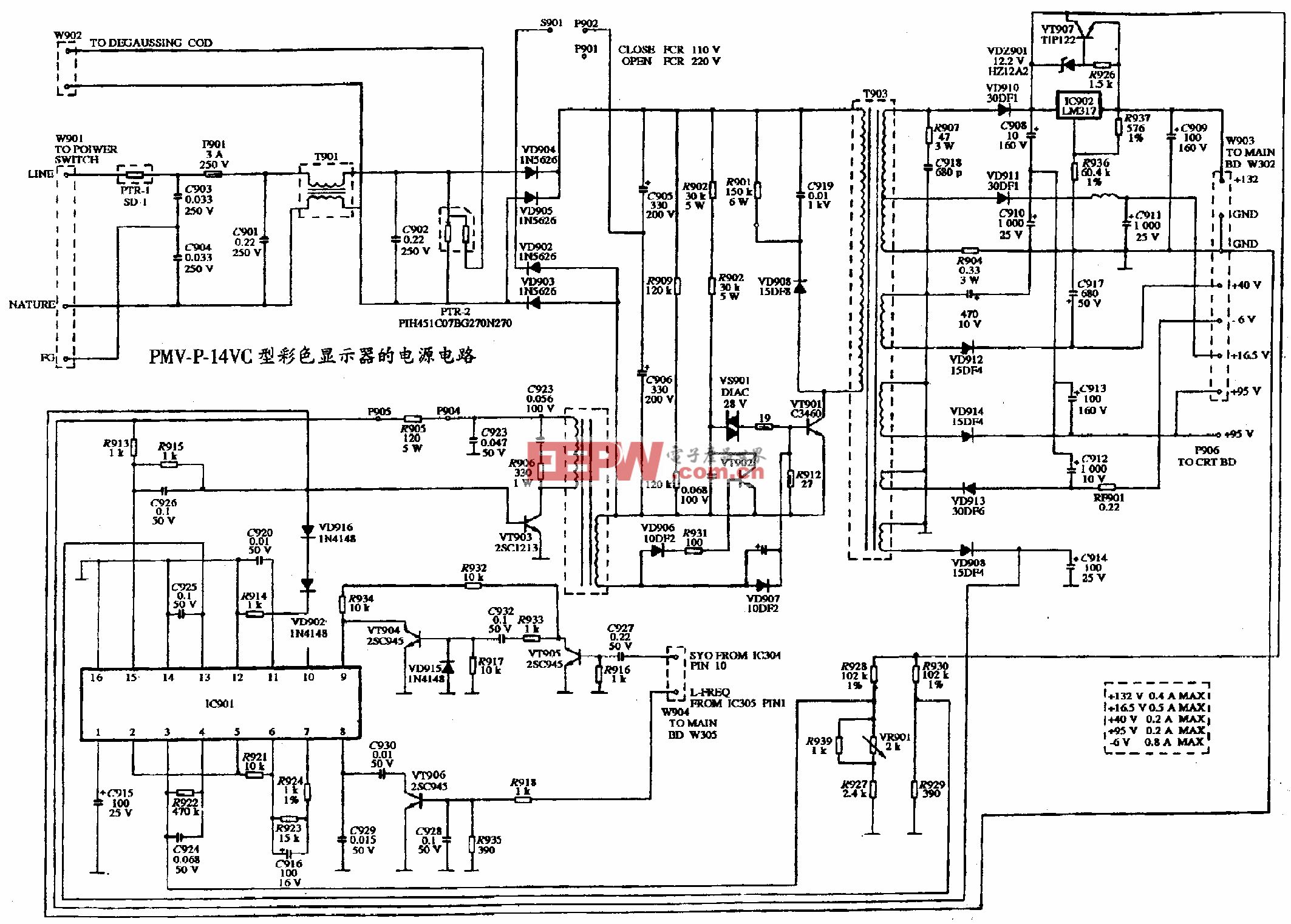

1 IXP2400的體系結構

網絡處理器(Network Processor)是一種面向包結構處理的專用器件。IXP2400是Intel公司第二代高性能網絡處理器之一,是在第一代網絡處理器的基礎上,實現了高性能的并行處理結構,從而能夠實現復雜的算法、深入查看包內容、進行流量管理及以線速(2.4 Gb/s)轉發包等;并首次采用Intel的超任務流水線技術,允許將1個包處理任務分解為多個易于銜接的、有序的子任務,并確保微引擎間通信的低時延。在體系結構上,具有以下特點:

(1)多處理單元結構,各單元獨立運行,并以硬件實現多線程技術,線程間無任何需切換開銷。

(2)以軟件流水線的形式分派任務到各處理單元,各處理單元可并行操作。

(3)ALU采用優化過的指令,專用于數據包處理,1條指令能在1個時鐘周期內完成。

(4)具有一些完成特殊功能的硬件單元,如CRC校驗、Hash計算、甚至加/解密運算單元,用于加速專用處理。

IXP2400的體系結構如圖1所示。

其主要功能部件如下[1]:

(1)XScale:32位的RISC高性能通用處理器,用于初始化、管理整個芯片,同時能執行高層網絡處理任務,如復雜的算法處理、路由表維護等。

(2)Microengine(MEv2):8個相互獨立的32 bit可編程微引擎,是處理數據的主要場所,各微引擎間用寄存器通信。每個微引擎主要包括:1個存放該微引擎運行程序的控制存儲器、8個硬件支持的線程、數據通路和控制狀態寄存器、1個ALU及1個CRC單元等。

(3)存儲器控制器:用于控制訪問片外RAM,包括SRAM、DRAM。SRAM主要用于存儲各種控制信息,如路由表等;DRAM主要用作數據處理的緩沖區。

(4)Scratch:片內的16 KB通用存儲器,存放各種經常需快速查找的數據。

(5)Hash:能對48 bit、64 bit或128 bit的數據作Hash運算,并生成索引。

此外,IXP2400中還采用了一些如硬件隊列等技術來提高ALU的處理速度。

2 IPSec的工作原理

IPSec的安全服務是通過在IP層對所有數據流使用密碼和安全協議聯合實現的,能保證應用程序通信的安全性。它能應用于防火墻和路由器等網關設備,對上層應用是透明的。

IPSec利用2種通信安全協議[2]:認證頭(AH)和封裝安全載荷(ESP)。還有用于密鑰交換和管理的Internet密鑰交換協議(IKE)[2]和相應的認證/加密算法等協議組件。AH和ESP既可用于保護一個完整的IP包,也可以用來保護IP包中的上層數據。此外,還可以組合使用,實現不同的安全保護級別。AH和ESP使用2種工作模式[3]:傳輸模式和隧道模式。

由于IPSec體系設計與算法無關,因而可以為不同的通信對等體選擇不同的安全算法。為維護這些動態存在的安全策略,在實現IPSec時,需要定義相應的安全策略數據庫(SPD),其中的每1條記錄就是1條安全策略。

為正確處理具有IPSec功能的IP包,IPSec通信對等體需要將經協商一致后所采用的安全協議、工作模式、加密/認證算法、密鑰等信息與所建立的鏈路結合起來,才能為不同的數據流提供不同的安全保護。其實現方法就是在IPSec通信對等體間建立安全關聯(SA)。SA是通信對等體之間為進行安全通信而協商的一種約定。SA可由1個三元組唯一標識,表示為安全參數索引(SPI),目的IP,安全協議標識>。

為維護所有活動的SA參數,在實現IPSec時,需要定義相應的SA數據庫(SAD)。IKE的主要功能就是在IPSec通信對等體間動態進行通信參數協商[4],并提供經認證的密鑰信息,從而建立起SA,對其進行維護和管理。

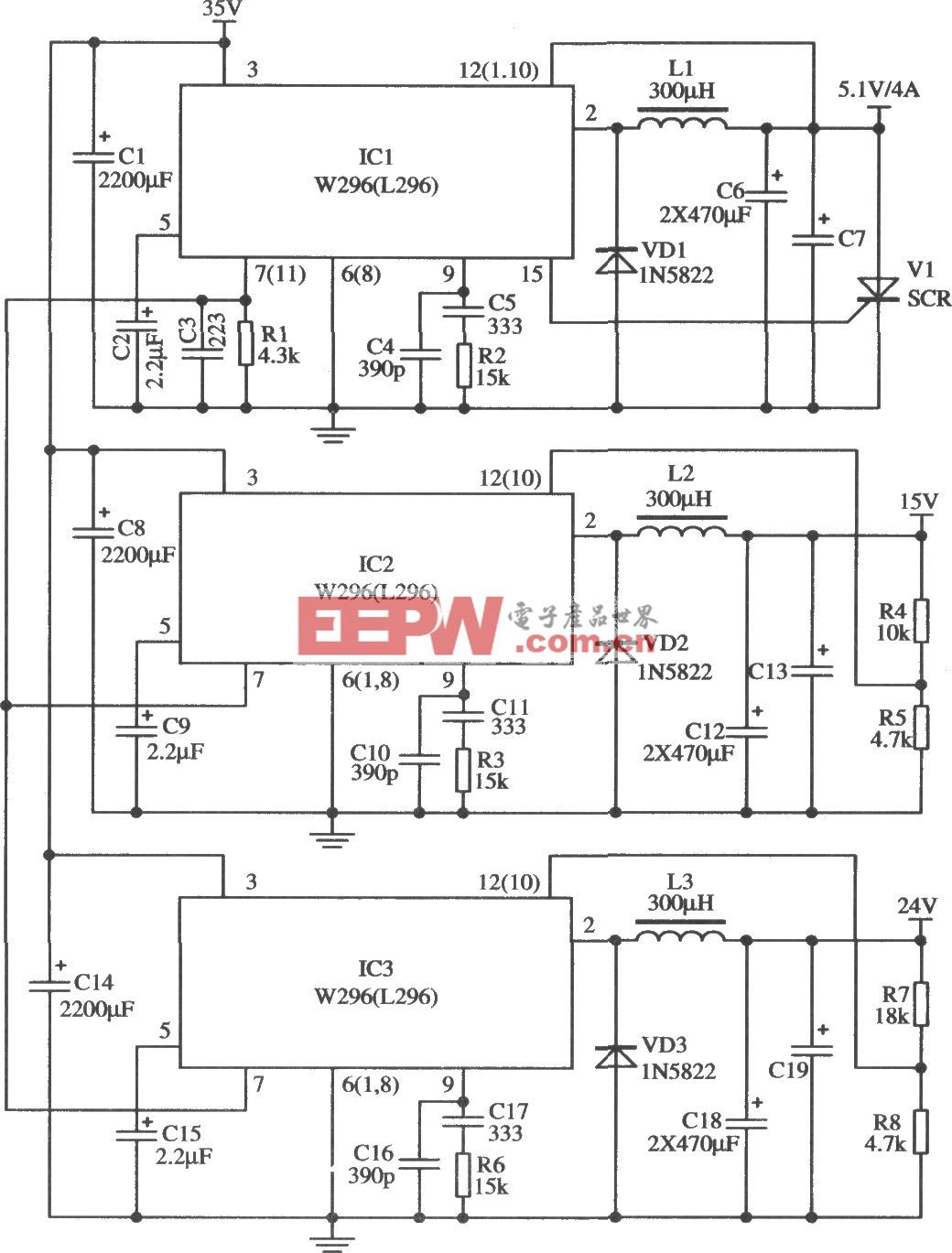

3 IPSec在IXP2400中的實現

3.1 程序設計

網絡應用程序中,網絡信息的處理通常包含在以下2個邏輯層面中[5]:

(1)數據層面:負責高速處理、轉發數據包。因所有要處理的數據包都必須通過該層面,故其性能直接影響到整個程序的性能。

(2)控制層面:主要處理協議信息,并負責創建、配置及更新各種表和數據集,供數據層面查找使用。如處理含路由信息的RIP、OSPF包,然后更新IPv4轉發表,供數據層面使用。

網絡處理器就是完成這2個層面的功能。

在IXP2400中,將數據層面分為快速通道和慢速通道。快速通道主要由各微引擎構成,完成絕大多數包的正常處理,如IP包轉發等;慢速通道主要由XScale構成,處理少數需復雜處理的包,如異常包、包分段等。考慮到處理速度的要求,在快速通道中通常將處理任務以軟件流水線形式分配到多個微引擎中實現,每個微引擎以編程方式實現所指定的任務。當一個微引擎完成其任務后,將包傳到下一微引擎繼續處理,直至完成整個任務。每個微引擎的流水線又可由若干流水線級構成,這些流水線級是順序執行的。由于每個微引擎有8個線程并發(甚至有數個微引擎的線程在并行)執行相同任務,因而要按序正確處理數據包,就必須考慮各線程訪問臨界區代碼的同步問題。為保證指令盡可能少,以達到線速要求,一種處理方法就是:在一個微引擎中讓各線程順序執行,并且每個線程順序執行所有流水線級。如某個流水線級的功能對所處理的包并不要求,則在執行到該流水線級時必須進入等待,當線程下一次獲得運行時再執行下一流水線級;如有數個微引擎在并行執行同一任務,則必須考慮微引擎間的執行順序。可見,將少數包要求的復雜處理任務交給XScale,能有效減少微引擎不必要的等待時間,加快數據的處理速度。

對于控制層面,因所要處理信息復雜、廣泛,涉及的指令范圍廣,數據層面中的快速通道是難以處理的,因而應放在XScale中實現[5]。

通常,將快速通道處理任務按邏輯劃分為若干功能塊,在可編程的微引擎中,每一塊實現稱為一個微功能塊(microblock)。而將運行在XScale中的微功能塊對應的慢速通道處理部分稱為核心組件(Core Component),完成相應微功能塊的配置、初試化及維護共享數據結構,并處理微功能塊發送的異常包或信息。此外,各種路由協議也運行在XScale中,處理各種協議信息。這樣實現了數據層面和控制層面的分離,兩層面間可用標準API通信。

將所有任務放在一個IXP2400中實現,可能滿足不了線速要求,因而通常將任務分配到2個IXP2400來實現。這樣對于需要較多指令的微功能塊,可指定多個微引擎并行運行,適當增加每個微引擎的執行時間。

3.2 系統功能

綜上述分析,實現方案的系統框圖如圖2所示。

評論