DM642無線圖像傳輸的TS流傳輸新技術

摘要:介紹一種基于M642的視頻無線傳輸系統,在此基礎上重點探討了關于TS流傳輸的問題,提出了使用McBSP和GPIO方式分別實現TS流傳輸,并給出了一種改進的乒乓方式。實驗結果證明,采用McBSP和GPIO都可以解決TS流傳輸問題,但在速度和實現難度方面采用GPIO表現更好,改進型的乒乓結構也在一定程度上提高了程序的效率。

關鍵詞:TS流傳輸;DM642;視頻無線傳輸系統;EDMA;McBSP;GPIO

引言

無線通信技術因其免去了使用實體接線,為生活帶來諸多便利,因此受到廣大消費者的青睞。其中短距離無線通信技術作為無線通信的一個發展趨勢,越來越受到人們的關注。數字圖像信息及其處理技術正在發揮著越來越重要的作用,在人們生活中的地位也將越來越高。原來的民用設計普遍采用ASIC方式,如STi5517、STi5518等,但由于禁運等原因無法達到工業級及以上的標準。本設計采用的DM642和FPGA靈活性高,升級優化方便,且達到了工業級等級以上。本文主要介紹TS流傳輸的新方式,實現信源板中TS流實時傳輸到信道板上。

1 簡介

1.1 基于DVB-T無線視頻傳輸系統

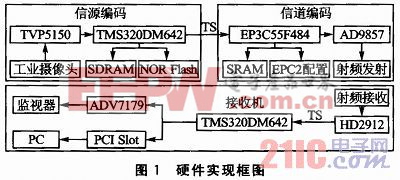

無線視頻傳輸系統的硬件實現框圖如圖1所示。本系統硬件分為4個組成部分:信源編碼部分、信道編碼調制部分、射頻部分和接收機部分。

攝像頭采集視頻信號,并輸出PAL制的模擬電視信號。視頻解碼器將AV視頻信號數字化和解碼,轉化為YUV(4:2:2)格式輸出。TMS320DM 642將原始視頻以MPEG-2格式進行編碼,并且將編碼數據封裝為TS數據流。TS數據流以SPI并行數據格式傳遞給信道解碼部分。

信道編碼部分通過FPGA(EP3C55F484)對數據進行DVB-T編碼和中頻調制,調制信號經過模擬上變頻完成射頻調制。

接收機部分通過接收射頻信號并對其進行模擬下變頻,提取出感興趣的中頻信號,利用信道解調器對其進行信道解碼。解碼后的信源數據流以TS流格式傳送給TMS320DM642處理器。處理器先進行TS解包,再對MPEG-2數據流解壓縮。根據系統不同設置,可以通過PCI接口發送至PC端進行后端數據處理,或通過視頻編碼器將視頻信號還原為模擬電視信號。

1.2 傳送流(TS流)

TS流是由打包的視頻、音頻基本碼流再經過打包形成的復合碼流,每包長度為188字節,或由PS流分段截取,適用于誤碼較大的應用環境。傳送流的系統層可分作兩個子層:一個是相應于特定數據流操作(PES分組層,可變長度),該層是為編解碼的控制而定義的邏輯結構,

PES頭包括流的性質、版權說明(該節目是原始節目還是復制節目)、加入時間標簽PTS和DTS、說明DSM的特殊模式等;另一個是相應于多路復用操作(TS分組層,188字節固定長度結構),該層是針對交換和互操作而定義的,在TS頭中加入同步、說明有無差錯、有無加擾,加入連續計數和不連續性指示(因為節目流的包相互交叉),加入節目參考時鐘PCR以及包識別PID等。兩個子層間的復用關系是將PES結構切割成一個個小包,作為TS包的凈荷嵌入到TS流結構中而建立起來的,這種結構可以很方便地實現直接從傳送流中解出原始音視頻數據,也可從一個或多個傳送流中抽取想要的基本流來進行解碼,或構造新的傳送流再次傳輸,還可以依據通信信道的質量在TS流與PS流間作切換。

1.3 數據在DM642接口的傳輸

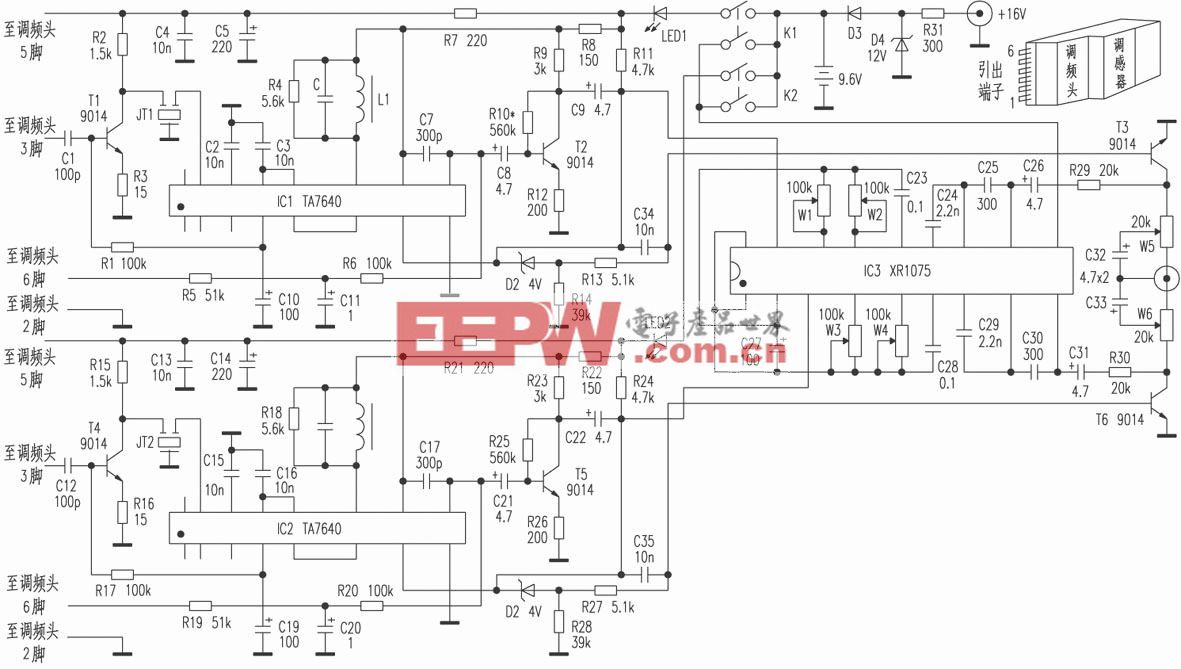

I2C總線傳輸為140kb/s,速度慢,接口簡單,適合于各種芯片參數的配置或EEPROM訪問等數據量小的通信。視頻口傳輸為27M×20b/ s,數據較快,接口復雜,功能單一,一般只用于DSP與視頻編/解碼器之間的視頻數據傳輸。網口傳輸為10M/100M,通信協議復雜,若用FPGA實現,則接口也復雜,適合于DSP與PC機間的數據傳輸。McBSP傳輸為40 Mb/s,如果用FPGA實現接口較為簡單,適合于DSP與FPGA低速數據傳輸。GPIO傳輸為10M×n,n是GPIO的引腳數目,接口極其簡單,傳輸速度較快。如DM6437共有111個GPIO引腳,若用3個32位的GPIO則可達到960 Mb/s。即使用1個32位的GPIO bank也可以達到320 Mb/s,能夠滿足一般的數據傳輸需求。DM642有16個GPIO口,速度也可達到160 Mb/s,滿足設計要求。圖2即是GPIO方式傳輸TS流需要的時序。

如果利用任務或中斷的方式傳輸數據,因為數據量大,勢必增加CPU的負擔,這種負擔很有可能是CPU無法承受的。例如使用任務來傳輸,若數據為8 MB/s,則這個任務占用CPU 80%的時間,這是本應該占據大部分時問的圖像壓縮算法無法忍受的,并且時常可能被突如其來的中斷打斷而丟失數據。若利用中斷來同步傳輸,而使CPU大部分時間在中斷中,亦是不現實的。這里采用DSP中的增強型的DMA模塊(EDMA),在CPU不參與的情況下完成數據傳輸,只有傳輸完成才進入中斷,如此則解放出CPU,以使算法占用它。

pid控制相關文章:pid控制原理

評論