一種基于稀疏矩陣的多核并行擾碼方法

1.1 基于稀疏矩陣的多核并行擾碼

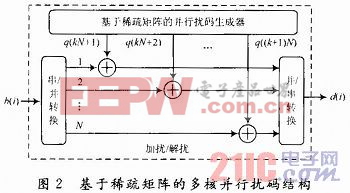

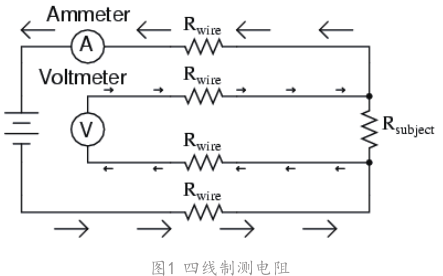

基于稀疏矩陣的多核并行擾碼結構如圖2所示。基于稀疏矩陣的并行擾碼生成器產生了偽隨機序列q,且同時輸出序列q中N個相鄰的偽隨機碼。此外,輸入信號b(i)經過串/并轉換后得到N路并行信號,然后分別送入對應序號的處理器核,在單個處理器核內,生成的偽隨機碼與輸入信號進行模二加運算,得到輸入信號的擾碼輸出;最后,并行擾碼輸出經過并/串轉換得到串行擾碼輸出d(i)。本文引用地址:http://www.j9360.com/article/155094.htm

圖2中q(i)表示偽隨機序列的第i個元素;k為非負整數;加法器表示模二加運算,則第i時刻擾碼輸出d(i)的數學表達式為:

d(i)=b(i)⊕q(i) (1)

從圖2及式(1)可以看出,基于稀疏矩陣的并行擾碼生成器是加擾,解擾過程中的重要組成部分。接下來詳細介紹如何實現基于稀疏矩陣的并行擾碼生成器。

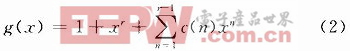

假設并行擾碼生成器輸出的偽隨機序列q為m序列,則q可由r級線性反饋移位寄存器產生,且其循環周期L=2r-1。r級線性反饋移位寄存器的生成多項式可寫為:

式中c(n)取值為0或1。

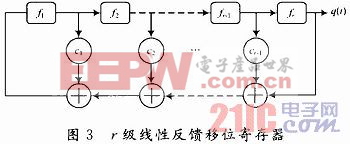

以式(2)作為生成多項式,圖3給出了相應的r級線性反饋移位寄存器結構。

圖中,q(i)表示第i時刻生成的偽隨機碼;fn代表寄存器;cn代表乘法器,加法器表示模二加運算,則i時刻的線性反饋移位寄存器狀態為:

Fi=[f1i,f2i,…,fri]T (3)

下一時刻,線性反饋移位寄存器的狀態為:

評論