基于SJA1000 IP核的CAN總線通信系統

(3)位數據流處理器程序

位數據流處理器程序執行總線上的錯誤檢測、仲裁、填充和錯誤處理等功能。它主要由接收模塊、發送模塊、錯誤管理模塊、CRC校驗、驗收濾波、FIFO6個子模塊組成。CRC校驗、驗收濾波、FIFO子模塊將單獨設計成子程序供位數據流處理器程序調用。

(4)CRC校驗程序

CRC校驗程序主要用來完成CAN總線網絡中循環冗余校驗碼功能。

(5)驗收濾波器程序

驗收濾波器程序的功能是由驗收代碼寄存器(ACR)和驗收屏蔽寄存器(AMR)共同完成的。驗收代碼寄存器將接收到幀中的標識碼內容與其自身的內容逐位的進行比較,以決定是否要接收這條報文,驗收完全通過后則保存到FIFO中。驗收屏蔽寄存器則決定在比較中起作用的驗收代碼寄存器的位(驗收屏蔽寄存器為0,則相應的驗收代碼寄存器的位相關;驗收屏蔽寄存器為1,則對應的位無關)。

(6)先入先出FIFO存儲器程序

先入先出FIFO存儲器程序的功能是先對接收的報文進行存儲,并在CPU要求讀出數據時,將接收到的數據通過數據總線從控制器中讀出。FIFO模塊特點是先進入先輸出,后進入后輸出。本文中的FIFO存儲器是同步的,只有一個時鐘信號。

(7)頂層控制程序

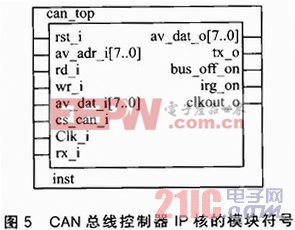

頂層控制程序(can_top)是整個CAN總線控制器SJA1000 IP核的最上層模塊,主要負責調用并控制以上6個程序模塊協同工作。

程序全部設計完后,通過使用QuartusII9.0的編譯和綜合將整個程序封裝成模塊符號的形式,如圖5所示。這樣方便存后面的CAN總線通信系統設計中調用。本文引用地址:http://www.j9360.com/article/154098.htm

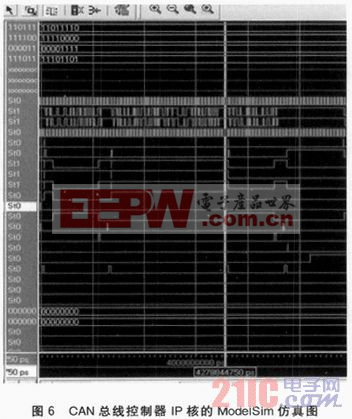

對CAN總線控制器IP核的仿真是在ModelSim軟件測試平臺中進行的,其仿真結果如圖6所示。

從圖6中我們可以得出:白色豎線處發送成功狀態(tx_successful)置1,豎線前面一段時間內,CAN總線控制器IP核的發送狀態(transmit _status)為1,接收狀態(receive_status)為0,這說明控制器前面已成功地完成了一次發送操作;隨后硬同步(hard_sync)置1,發送狀態為

0,接收狀態為1,控制器又開始一次接收操作,并在接收完后發送應答位(send_ack置1),且置info_empty為1。

3 SJA1000 IP核的CAN總線通信系統設計

基于SJA1000 IP核的CAN總線通信系統是將8051IP核、數據RAM、程序ROM以及CAN總線控制器IP核一同設計到FPGA芯片內,從而構成SPOC系統的。基于IP核復用技術的CAN總線硬件連接圖如圖7所示。和傳統的CAN總線系統構架不同,本文的設計采用的是FPGA而不是單片機作為CAN總線通信系統的控制器。相對于單片機等微處理器而言,FPGA有著其獨特的優勢:I/O口資源豐富,可以很容易地實現更多的擴展功能;而且在電路設計中除了極少數必要的外圍器件外,其余的電路都可以集成設計到FPGA中。這樣做可以減少由于器件較多而產生的電磁干擾的可能性,而且還可以減少系統的體積和功耗、提高系統的可靠性。

在CAN 2.0B協議中,為了能夠達到設計透明度以及實現靈活性,根據ISO/OSI參考模型,CAN被細分為以下不同的層次:

①數據鏈路層。其中包括邏輯鏈路控制子層(LLC)和介質訪問控制子層(MAC)。

②物理層。物理層的作用是在不同節點之間根據所有的電氣屬性進行位的實際傳輸,它是由CAN總線驅動器和電氣線路構成的。

邏輯鏈路控制子層(LLC)和介質訪問控制子層(MAC)的功能,即報文分幀、仲裁、應答、錯誤檢測和標定、報文濾波、過載通知以及恢復管理都是由CAN總線控制器實現。因此,CAN總線控制器IP核(CAN_Module)主要完成LLC和MAC子層的功能。

4 CAN總線通信系統的測試與驗證

4.1 硬件電路的設計

CAN總線SOPC硬件連接圖如圖7所示,下面對圖7所示的兩個部分進行簡單介紹。

4.2 系統的控制部分

控制部分選用的是KX_7C5E型實驗電路板,該實驗板中的FPGA目標芯片是Altera公司的Cyclonc III型EP3C5E144C8。其中FPGA芯片包含有8051單片機IP核、CAN總線控制器IP核、內部程序ROM、內部數據RAM和鎖相環(PLL)等模塊。

4.3 CAN總線收發器部分

因為FPGA芯片的供電電壓和I/O口輸出電平為+3.3 V,所以在設計中CAN總線收發器選用的供電電壓也必須是3.3 V的。CTM1050T CAN總線收發器模塊是集成電源隔離、電氣隔離、CAN總線收發器和CAN總線保護于一體的CAN總線隔離收發器模塊。有了CAN總線隔離收發器,就可以很好地實現CAN總線上各節點電氣、電源之間的完全隔離和獨立,這樣可以提高各個節點的穩定性和安全性。該模塊的TXD、RXD引腳不需要外接其他元器件就可以很好地兼容+3.3 V及+5 V的CAN總線控制器。因此在圖7中我們將FPGA的I/O口與CTM1050T的引腳直接相連,故沒有設計任何外圍電路。

最后通過使用KX_7C5E型實驗電路板、CAN總線收發器、USBCAN-II、CAN總線實驗臺實驗,能夠進行基本的收發,驗證了系統的可行性。

結語

本文已成功驗證了基于SJA1000 IP核的CAN總線通信系統的可行性,該設計充分展現了片上可編程系統的靈活性和可移植性,減小了系統體積和功耗,完全可以代替原有傳統的CAN總線系統方案。

評論