HDB3編碼器ASIC的設計

2.2 插入“B”模塊

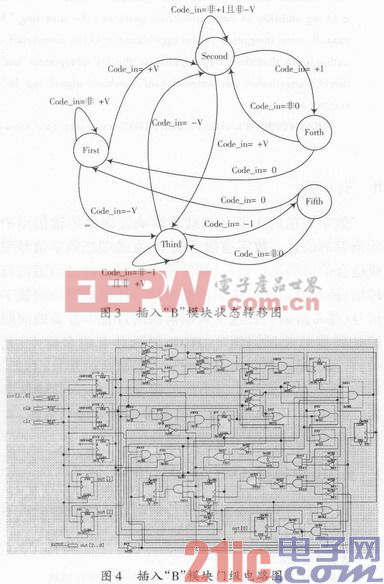

信息代碼經過上級模塊(插入“V”模塊)以后,輸出的代碼將是極性正負交替的碼型。插入“B”模塊的功能是:當兩個連續的“V”之間有偶數個“1”時,要將該小段中第一個“0”替換成“B”,其符號與前一非“0”符號相反;當兩個連續的“V”間有奇數個“1”時,則無須替換。本模塊的設計精髓是:設計成可綜合的狀態機,利用狀態機的方法將信息代碼編成HDB3的碼。此設計共5個狀態,并且將插入的破壞碼“B”的極性記錄下來,以便下級模塊進行“V”碼極性的糾正。在第一個狀態中,如果接到的數據是“+V”或“-V”,信息代碼原樣輸出,分別轉移到第2、第3個狀態;如果是其他符號的數據,信息代碼也原樣輸出,回到第一個狀態。在第二個狀態中,當有非“+1”符號輸入時,信息代碼原樣輸出,回到第二個狀態;當有“+1”輸入時,說明兩個相鄰的“V”之間有偶數個“1”,轉移到第4個狀態。在第四個狀態中,當有“0”輸入時,則讓此刻的“0”替換成“-B”,回到第一個狀態,重新開始判斷兩個連續的“V”之間是否有偶數個“1”;當有非“0”符號輸入時,回到第二個狀態。第三、第五個狀態工作方式與以上類似。狀態轉移圖見圖3,模塊門電路見圖4。本文引用地址:http://www.j9360.com/article/153462.htm

評論