嵌入式系統降低功耗的方法研究

摘要 低功耗嵌入式系統設計的能量消耗問題是近幾年來在嵌入式系統設計中普遍關注的難點與熱點,它嚴重制約著嵌入式系統的應用及發展。本文以降低嵌入式系統所耗電能為目標,提出了嵌入式系統降低功耗的綜合措施,并對低功耗嵌入式系統各種經典措施進行優化改進,使之充分發揮降低功耗的作用。最后闡述了該解決措施尚存在的一些關鍵問題,并對低功耗嵌入式系統的前景和發展進行了評述。

關鍵詞 低功耗硬件設計 低功耗軟件設計 DVS DPM

引 言

隨著嵌入式系統應用的迅速發展,PDA和移動電話等便攜式裝置深入到生產生活的各個角落,嵌入式系統市場有迅速增長趨勢。嵌入式系統一般是由電池來供給電能的,而且大多數嵌入式設備都有體積和重量的約束。減少電能消耗不僅能延長電池的壽命,縮短用戶更換電池的周期,而且能提高系統性能與減小系統開銷,甚至能起到保護環境的作用。

1 嵌入式系統功耗分析

研究微處理器的低功耗設計技術,首先必須了解它的功耗來源。如圖1所示,從高層次仿真得出的結論可以看出,通過開關級功率模擬所獲得的高性能CPU的功率分布關系。其中,時鐘功耗所占比例最大,包括時鐘發生、驅動器、時鐘樹、鎖存器和所有時鐘負擔的器件;數據通路的功耗僅次于時鐘,主要包括執行單元、總線和寄存器文件;片上存儲器的功耗主要由存儲器的大小以及存儲陣列的電路和物理結構所決定;控制單元和I/O的功耗通常占整個芯片功耗的一小部分。

2 嵌入式系統低功耗設計

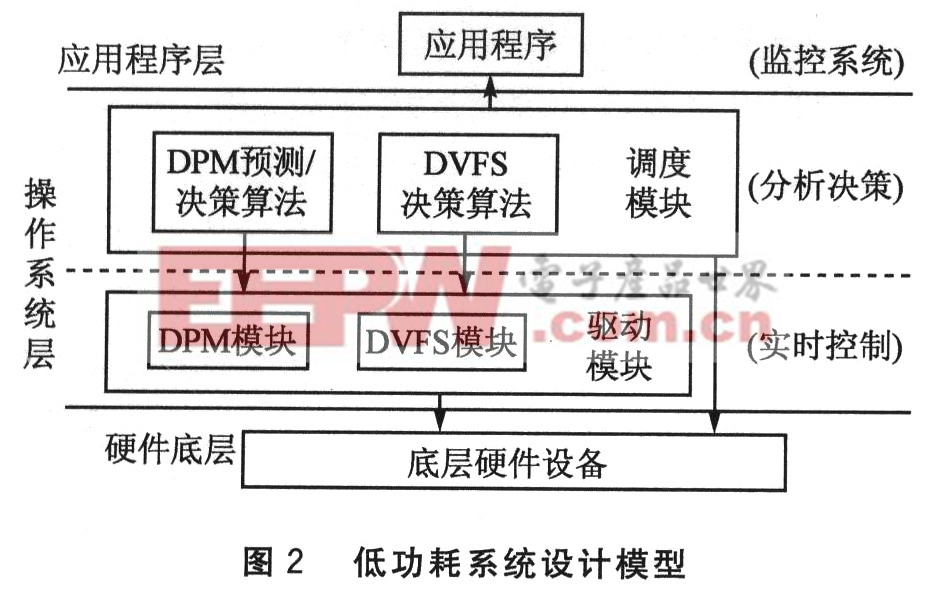

低功耗設計是一個復雜的綜合性課題。就流程而言,包括功耗建模、評估以及優化等;就設計抽象層次而言,包括自硬件底層至應用程序層的所有抽象層次,而目前低功耗設計大都在操作系統層實施,如圖2所示。同時,功耗優化與系統速度和面積等指標的優化密切相關,需要折中考慮。下面根據各部分在嵌入式系統中的不同層次,討論常用的低功耗設計技術及具體應用。

2.1 低功耗硬件設計

低功耗硬件設計是嵌入式系統降低功耗的重要內容。因此,需要從系統內部結構設計、系統時鐘設計和低功耗模式等幾方面采用特定的方法(例如,門控時鐘和可變頻率時鐘、并行結構與流水線技術、低功耗單元庫、低功耗狀態機編碼、Cache低功耗設計等)來實現系統硬件節能設計。下面介紹門控時鐘和可變頻率時鐘的應用。時鐘是惟一在所有時間都充放電的信號,而且很多情況下引起不必要的門的翻轉,因此降低時鐘的開關活動性將對降低整個系統的功耗產生很大的影響。門控時鐘包括門控邏輯模塊時鐘和門控寄存器時鐘。門控邏輯模塊時鐘對時鐘網絡進行劃分,如果在當前的時鐘周期內,系統沒有用到某些邏輯模塊,則暫時切斷這些模塊的時鐘信號,從而顯著降低開關功耗。圖3為采用“與”門實現的時鐘控制電路。門控寄存器時鐘的原理是當寄存器保持數據時,關閉寄存器時鐘,以降低功耗。門控時鐘易引起毛刺,必須對信號的時序加以嚴格限制,并對其進行仔細的時序驗證。

評論