基于嵌入式微處理器和FPGA的高精度測頻設計

引 言

本文引用地址:http://www.j9360.com/article/152401.htm本課題來源于一個無紙記錄儀的項目。在該項目中要求無紙記錄儀中有一路通道將工業現場采集到的頻率信號測量并顯示出來。

傳統的測頻系統大多采用單片機加邏輯器件構成,而這類測頻系統存在測頻速度慢、準確度低、可靠性差的缺點,故而使測量儀表達不到工業現場的要求。鑒于此,本文設計了一種基于嵌入式微處理器SEP 3203和FPGA的測頻系統。將嵌入式微處理器靈活的控制功能與FPGA的設計靈活、高速和高可靠性的特點有機結合,從而達到工業現場的實時測量要求,而且該測頻系統具有可重構性。

2 測頻原理

常用的直接測頻方法主要有測頻法和測周期法2種。測頻法就是在確定的閘門時間tw內,記錄被測信號的變化周期數(或脈沖個數)Nχ,被測信號的頻率為fχ=Nχ/tw。測周期法需要有標準信號的頻率fs,在待測信號的一個周期內tχ,記錄標準頻率的周期數Ns,被測信號的頻率為fχ=fs/Ns。這2種方法的計數值會產生±1個字的誤差,并且測試精度與計數器中記錄的數值Nχ或Ns有關。為了保證測試精度,一般對于低頻信號采用測周期法,對于高頻信號采用測頻法,這樣測試時很不方便,所以人們提出了等精度測頻的方法。

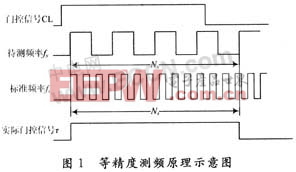

等精度測頻方法是在直接測頻方法的基礎上發展起來的,他的閘門時間不是固定的值,而是被測信號周期的整數倍,即與被測信號同步,消除了對被測信號計數所產生±1個字的誤差,達到了在整個測試頻段內保持等精度測量。其測頻原理如圖1所示。

在測量過程中,有2個計數器分別對標準信號和被測信號同時計數。首先給出閘門開啟信號(預置閘門上升沿),此時計數器并不開始計數,而是等到被測信號的上升沿到來時,計數器才真正開始計數。然后預置閘門關閉信號(下降沿)到時,計數器并不立即停止計數,而是等到被測信號的上升沿到來時才結束計數,完成1次測量過程。從而實現了實際門控信號與被測信號的同步,進而消除對被測信號計數產生的一個脈沖的誤差。

設在1次實際閘門時間τ中計數器對被測信號的計數值為Nχ,對標準信號的計數值為Ns。標準信號的頻率為fs,則被測信號的頻率為:

fχ=(Nχ/Ns)×fs (1)

3 誤差分析

由式(1)可知,若忽略標頻的誤差,則等精度測頻可能產生的相對誤差為:

δ=(fχ-fe/fe)×100% (2)

其中,fe為被測信號頻率的準確值。在測量中,由于fχ計數的起停時間都是由該信號的上升沿觸發的,在閘門時間τ內對fχ的計數Nχ無誤差(τ=Nχtχ);對fs的計數Ns最多相差1個數的誤差,即│△Ns│≤1,其測量頻率為:

fe=[Nχ/(Ns+△Ns)]/fs (3)

將式(1)和式(3)代入式(2),并整理得:

δ=│△Ns│/Ns≤1/Ns-1/(τ×fs) (4)

由上式可以看出:測量頻率的相對誤差與被測信號頻率的大小無關,僅與閘門時間和標準信號頻率有關,即實現了整個測試頻段的等精度測量。閘門時間越長,標準頻率越高,測頻的相對誤差就越小。標準頻率可由穩定度好、精度高的高頻晶體振蕩器產生,在保證測量精度不變的前提下,提高標準信號頻率,可使閘門時間縮短,即提高測試速度。

4設計框圖及實現

(1)前級電路

即首先對待測信號進行處理使其達到與后級電路相兼容的脈沖信號。原理框圖如圖2所示。具體實現電路如圖3所示。

第一級電路是由開關三極管組成的零偏置放大電路,以保證放大電路具有良好的高頻響應,當輸入信號為零或負電壓時,三極管工作在截止狀態,輸出為高電平,當輸入為正電壓時,三極管工作在飽和狀態(導通),輸出電壓隨輸入電壓上升而下降。零偏置放大電路把如正弦波樣的正負交替波形變換成單向脈沖,這使得該電路可以測量任意方波信號、正弦波信號、鋸齒波信號、三角波信號等頻率。

第二級采用的是施密特非門觸發器CC74HC14,是對放大器輸出的信號進行整形,使其輸出的信號成為與后級電路相兼容的脈沖信號。

(2)后級電路

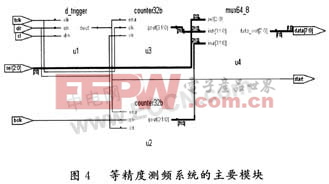

圖4為測頻系統的主要模塊。圖4中各模塊用硬件描述語言Verilog HDL描述,通過EDA工具(ModelSim,Synplify,QuartusⅡ)進行編譯、仿真、延時分析、管腳調整、綜合等步驟,最后燒錄到FPGA芯片中。將芯片與被測信號的放大整形模塊等外圍電路相連接,通過調試便完成了整個設計。

評論