基于AD9850的嵌入式信號源設計與實現

信號源是現代電子系統的重要組成部分,在通信、測控、導航、雷達、醫療等領域有著廣泛的應用,而且信號源作為現代電子產品設計和生產中的重要工具,必須滿足高精度、高速度、高分辨率、頻率可調等要求。傳統的RC或LC自激振蕩器方式的信號源組成較繁雜,調試較困難,不易實現程控,已不能適應新的要求;而由采用專用IC芯片構成的信號發生器,例如使用MAX038或ICL8038集成芯片外接分立元件,通過調節外接電容或電阻來設置輸出信號頻率,其輸出信號受外部分立器件參數的影響很大,且輸出信號頻率不能太高,同時無法實現頻率步進調節,不便于擴展和較高的使用要求。另外,采用FPGA+D/A可實現正弦信號發生器的設計,同時可實現頻率步進調節;但當輸出高頻信號時,需要高速D/A來配合工作,成本較高。頻率合成與鎖相技術的應用,可獲得高精度的信號源。目前,頻率合成技術是研制信號源的最關鍵技術。直接數字頻率合成技術(Direct Digital Frequency Synthesis,DDS)是從相位概念出發直接合成所需波形的一種新的頻率合成技術。DDS技術具有相對帶寬寬,頻率轉換時間短,頻率分辨率高,切換時相位能保持連續等優點,能實現各種調制波和任意波形的產生。易于實現全數字化的設計。廣泛用于高精度頻率合成和任意信號發生。

該設計采用直接數字頻率合成(DDS)技術,使用DDS芯片AD9850與超低功耗的MSP430F149單片機配合,可輸出精確控制的正弦波和方波信號。AD9850是AD公司推出的低功耗直接數字頻率合成器芯片,可以產生從直流到62.5 MHz的寬頻率信號,從投放市場至今已廣泛應用于雷達系統、低功耗頻率源中;MSP430是TI公司開發的一類具有16位總線的帶FLASH的單片機,該設計將AD9850與MSP430F149結合提出一種具有較高性價比和集成度、低功耗的嵌入式信號源設計方案。在控制流程中,通過4x 4矩陣鍵盤設定頻率值,MSP430為AD9850計算頻率控制字,并且將頻率控制字通過串行方式寫入其中,結合鍵盤上步進調節增量“1 Hz”,“10 Hz”,“100 Hz”鍵,使得頻率可以精確到步長為1 Hz的調節;產生正弦波時,經過低通濾波器濾除信號的高頻分量,通過增益可調的寬帶放大器放大輸出所需信號。如果接到AD9850內部的高速比較器上,即可直接輸出一個抖動很小的方波,系統通過字符型液晶屏1602顯示設定頻率和其他信息。實驗結果顯示,輸出信號頻率范圍在1 Hz~10 MHz,且無明顯失真;輸出信號頻率實現1 Hz,10 Hz,100 Hz三級步進調節,頻率精度0.01 Hz,頻率轉換速度1 ms,輸出幅度范圍1~10 V。

1 系統設計

1.1 DDS技術原理與結構

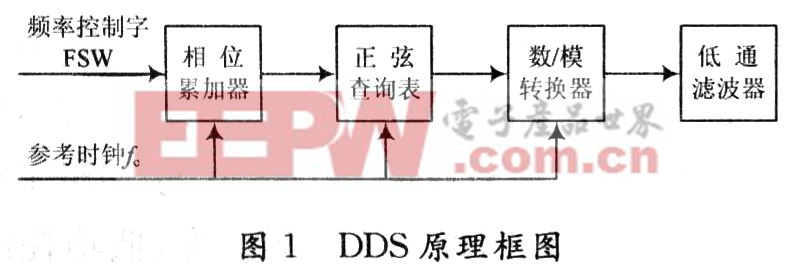

DDS技術是一種用數字控制信號的相位增量技術,具有頻率分辨率高,穩定性好,可靈活產生多種信號的優點。一個DDS信號發生器由相位累加器、波形數ROM表、D/A轉換器以及模擬低通濾波器LPF組成,原理框圖如圖1所示。DDS技術的核心是相位累加器。相位累加器在穩定時鐘信號的控制下產生讀取數據的地址值,隨后通過查表變換,地址值被轉化為信號波形的數字幅度序列,再由數/模變換器(D/A)將代表波形幅度的數字序列轉化為模擬電壓;最后經由低通濾波器將D/A輸出的階梯狀波形平滑為所需的連續波形。DDS信號發生器通過改變相位增量寄存器的值△phase(每個時鐘周期的度數)來改變輸出頻率。每當N位全加器的輸出鎖存器接收到一個時鐘脈沖時,鎖存在相位增量寄存器中的頻率控制字就與N位全加器的輸出相加。在相位累加器的輸出被鎖存后,它就作為波形存儲器的一個尋址地址,該地址對應波形存儲器中的內容就是一個波形合成點的幅度值,然后經D/A轉換變成模擬值輸出。當下一個時鐘到來時,相位累加器的輸出又加一次頻率控制字,使波形存儲器的地址處于所合成波形的下一個幅值點上。最終,相位累加器檢索到足夠的點就構成了整個波形。合成信號的波形取決于ROM表中的幅度序列,通過修改數據可以產生任意波形,如果要產生多種波形,只需把所需的多種波形數據存放到波形ROM表中。

DDS系統輸出正弦波的頻率計算公式為:

![]()

式中:fo為輸出正弦波的頻率;fo為系統的時鐘頻率;FSW為頻率控制字;N為相位累加器的字長,頻率控制字與輸出頻率成正比。由取樣定理,所產生的信號頻率能超過時鐘頻率的50 %,在實際應用中,為了保證信號的輸出質量,輸出頻率不要高于時鐘頻率的33 %,以避免混疊或諧波落入有用輸出頻帶內。

DDS的頻率分辨率定義為:

![]()

由于基準時鐘的頻率一般固定,因此相位累加器的位數決定了頻率分辨率;位數越多,分辨率越高。

該信號源采用DDS專用芯片AD9850產生正弦信號。AD9850采用CMOS工藝,其功耗在3.3 V供電時為155 mW,擴展工業級溫度范圍為-40~+80℃,采用28腳SSOP表面封裝形式,AD9850內含可編程DDS系統和高速比較器,能實現全數字編程控制的頻率合成。AD9850支持的時鐘輸入最高為125 MHz,頻率控制字的位數為32位。由式(2)可以計算出在125 MHz時鐘輸入時分辨率為0.021 9 Hz,該設計中選用30 MHz的有源晶振,故其分辨率按式(2)計算得0.006 9 Hz。

1.2 系統總體設計

該系統采用MSP430F149對DDS進行控制構成方波正弦波信號源的系統框圖如圖2所示。

該信號源由MSP430F149單片機、DDS芯片AD9850、低通濾波器(LPF)、4×4軟鍵盤、1602液晶顯示屏和外部參考時鐘源、寬帶放大器和穩壓電源等組成。其中,低通濾波器是信號源中的關鍵器件,負責濾除正弦輸出信號中的高頻、雜散信號和諧波信號;穩壓電源的+5 V電壓經過電平轉換后為MSP430和AD9850提供+3.3 V的電源電壓;外部參考時鐘源選用30 MHz有源晶振,MSP430F149與AD9850采用串行通信方式連接。

1.3 硬件設計

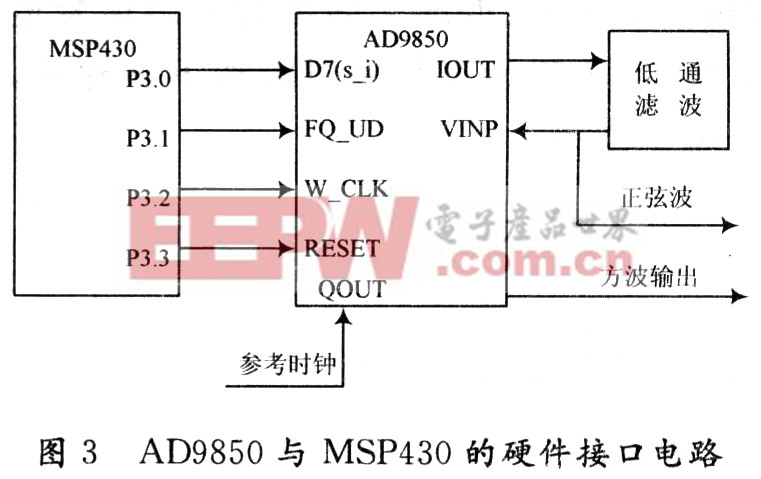

該信號源選用MSP430F149作為核心控制器,為了節省I/O資源,方便系統功能擴展,MSP430與DDS芯片AD9850之間采用串行通信方式,接口電路如圖3所示。AD9850與外圍元件的硬件連接圖如圖4所示,AD9851的正弦輸出信號端IOUT接至外部的低通濾波器,濾除高頻雜散和諧波后,一路信號經過寬大放大器AD811放大后輸出需要的正弦信號,另一路再回接到AD9851內部比較器的正向輸入端(VINP)以得到方波信號。其中:DGND為數字地;AGND為模擬地;VCC為模擬部分的電源電壓;VDD為數字部分的電源電壓。D7,FQ_UD,W_CLK,RESET分別接至MSP430的P3.0,P3.1,P3.2,P3.3上。為降低噪聲信號對放大器的影響,在低通濾波器與寬帶放大器之間接一級高速電壓跟隨器隔離,AD9850的輸出信號峰峰值為1~2 V,為增大AD9850輸出信號幅值,采用單位增益帶寬為140 MHz,Sr=2 500 V/μs的高速寬頻帶運放AD811進行信號放大,并且通過調節反饋電阻來改變增益,從而調節輸出信號幅度。放大電路的最大放大倍數,可以滿足一般的應用需求。

1.4 低通濾波器設計

低通濾波器是直接數字頻率合成器的重要組成部分,其性能的優劣直接影響整個直接數字合成器的特性。在整個DDS實現過程中,低通濾波器除了濾掉高頻信號之外,還有除去雜散的作用。DDS的雜散主要來源以下三個方面:

(1)ROM幅度量化誤差:相位轉化為幅度,是通過尋址ROM實現的,然而ROM地址中存有的波形幅度值字長是有限的,ROM存儲能力有限而引起的舍位誤差就是幅度量化誤差;

(2)相位截斷誤差:為了提高DDS的精度,DDS的相位累加器位數都取得非常大,但ROM的容量是有限的,因此只利用相位累加器的高M位ROM尋址,其低(N-M)位被截斷。由此引入的截斷誤差是DDS雜散的主要來源;

評論