BIST在SoC片上嵌入式微處理器核上的應用

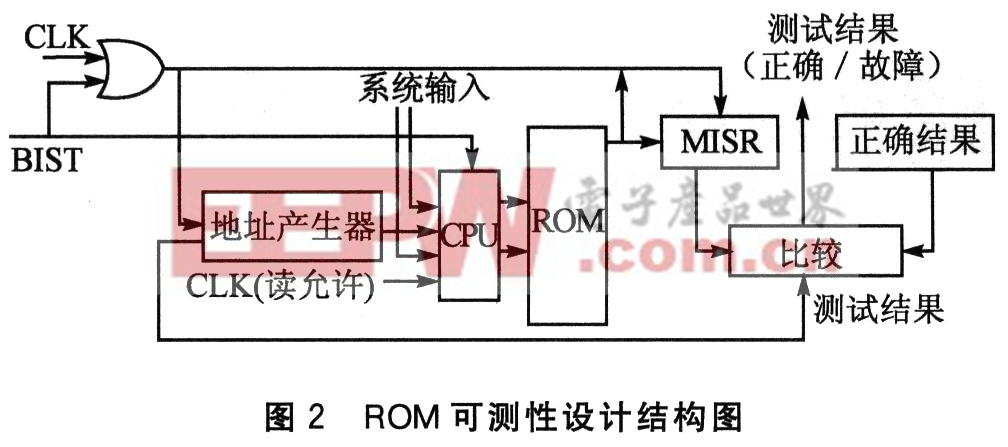

通常使用循環冗余校驗(CRC)電路實現ROM的測試,這種方法雖然測試結果很可靠,但是需要逐位讀取信息,而對ROM的訪問是每次32位,如果使用該方法則需要一個緩沖機制,并且速度會很慢。在此仍使用RAM測試中并行的數據壓縮,故障覆蓋率能夠達到要求,測試電路也比CRC電路簡單。測試電路如圖2所示。本文引用地址:http://www.j9360.com/article/152327.htm

BIST測試信號由TAP控制器的TDT口輸入,是整個測試電路的使能信號,測試過程經過觸發后,完全在電路內部完成,結束后通過一個I/O口報告測試結果。多輸入寄存器(MISR)作為TAP控制器的數據寄存器,測試初始化時設置為初始狀態。

2.2 LogicBIST

LogicBIST方法是利用內部的向量產生器逐個地產生測試向量,將它們施加到被測電路上,然后經過數字壓縮和鑒別產生一個鑒別碼,將這個鑒別碼同預期值進行比較。LogicBIST通常用于測試隨機邏輯電路,一般采用偽隨機測試圖形生成器來產生輸入測試圖形,應用于器件內部機制;采用MISR作為獲得輸出信號產生器。由于MI-SR的結構和多輸入序列的鑒別碼的固有特點,這是一個多對一的映射關系。不同的輸入序列通過MISR之后可能產生相同的鑒別碼,這被稱之為alias。

LogicBIST測試只能得到芯片能否通過測試的結果。一旦芯片不能通過測試,該如何確定芯片內部的故障點在何處呢?這就是診斷工作,不過LogicBIST對故障診斷的支持太弱,如果一塊芯片未能通過,單單憑錯誤的鑒別碼是很難確定故障點在何處的。有時會出現芯片內部多個故障點的共同作用使得鑒別碼反而是正確的現象,這被稱之為漏測試。它產生的概率非常小,也有算法來盡量減小漏測試發生的概率。其中一種方法是將正確的序列輸入,和正確的鑒別碼作單一映射,其他的錯誤輸人一定得到錯誤的鑒別碼。這種方法對MISR、PRRG以及CUT都需要具體分析,以改變其結構或者PRPG的生成順序。

結 語

本文介紹了SoC片上嵌入式微處理器核可測性技術的研究現狀;介紹了設計時在電路中植入相關功能電路,用于提供自我測試功能的技術,以降低器件測試對自動測試設備(ATE)的依賴程度。BIST技術可以實現自我測試,也可以解決很多電路無法直接測試的問題(因為它們沒有外部引腳)。

可以預見,在不久的將來即使最先進的ATE也無法完全測試最快的電路,這也是采用BIST的原因之一。但是BIST也存在一些缺點,如額外的電路會占用寶貴的面積,會產生額外的引腳和可能出現測試盲點等。BIST技術正成為高價ATE的替代方案,但是目前還無法完全取代ATE,他們將在未來很長一段時間內共存。

評論