一種時延設計方法與DSP實現

前面介紹的抽取和內插的結構對運算速度的要求是相當高的,這主要表現在抽取濾波器模型中的低通濾波器位于抽取算子之前,也就是說低通濾波器是在降速之前實現的;而對于內插器模型,其低通濾波器位于內插算子之后,也就是說內插器低通濾波器是在提速之后進行的。總之,無論是抽取器還是內插器,其抗混疊數字濾波均在高取樣率條件下進行,這大大提高了對運算速度的要求,對實時處理是極其不利的。下面將討論有利于實時處理的抽取器、內插器的多相濾波結構。

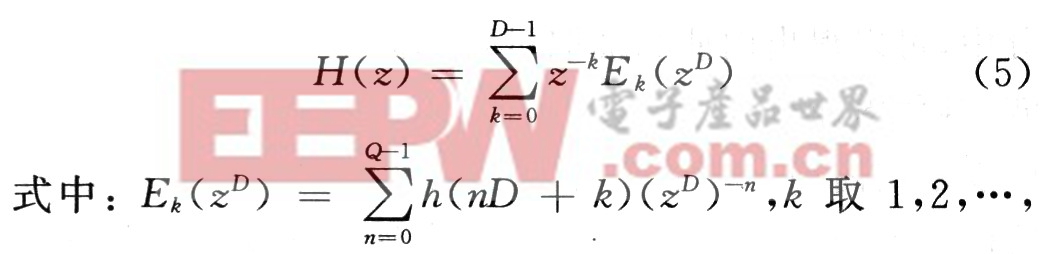

設數字濾波器的沖擊響應為h(n),它的z變換定義為:

式中,N為濾波器長度。如果將沖激響應h(n)按下列的排列分成D個組,如N不為D的整數倍,則將h(n)后補零,使得濾波器長度N為D的整數倍,即N/D=Q,Q為整數,則:本文引用地址:http://www.j9360.com/article/152292.htm

式中,N為濾波器長度。如果將沖激響應h(n)按下列的排列分成D個組,如N不為D的整數倍,則將h(n)后補零,使得濾波器長度N為D的整數倍,即N/D=Q,Q為整數,則:本文引用地址:http://www.j9360.com/article/152292.htm

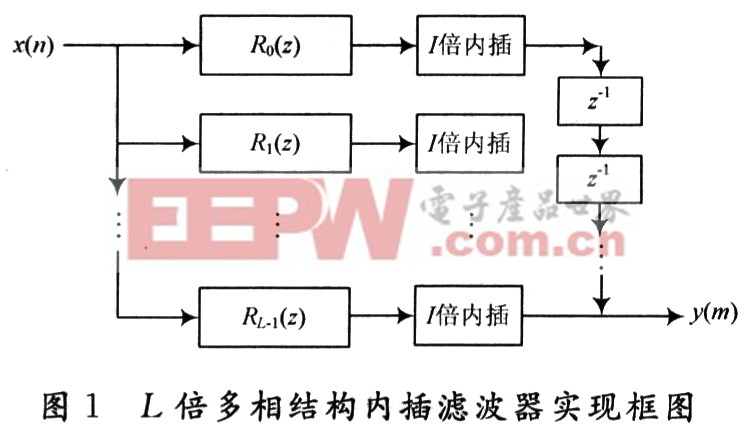

D-1。式(5)即為數字濾波器H(z)的多相濾波結構。針對本文的應用,此處給出一個I倍內插器多相濾波結構的實現框圖,如圖1所示。其中,Rk(z')=E(I-1-k)(z')。

由圖1可見,此時的數字濾波器Rk(z)位于內插器之前,即濾波是在數據流提速之前進行的,這就大大降低了對處理器的要求,提高了實時處理能力。此外,多相濾波器結構的另一個好處是每一分支濾波器的系數由原來的N個減少到N/I個,可以減小濾波運算的累積誤差,有利于提高計算精度,降低對處理器字長的要求。圖2是多相結構內插濾波器的開關結構形式。它可以更清楚地說明多相結構內插濾波器是如何工作的。對輸入速率為Fs的數據流,經L個子濾波器后,每個子濾波器的數據流速度依然是Fs,但整個內插濾波器的數據流速度提高為I?Fs,此時用速率為I?Fs的開關對輸出數據流進行選擇,即完成了I倍內插數據的獲取。同樣可以得出D倍抽取器多相濾波結構。

2 時延算法的DSP實現

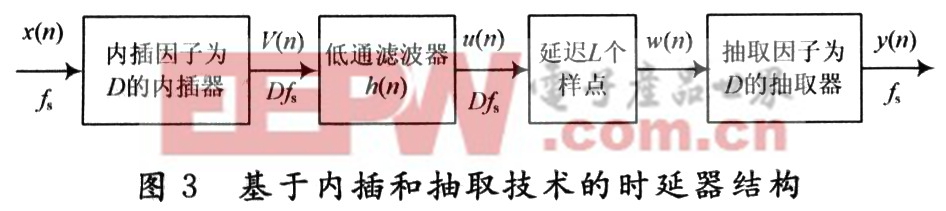

短波信道模擬器系統中常采用軟件無線電思想實現。軟件無線電的宗旨就是盡可能地簡化射頻模擬前端,使A/D轉換盡可能地靠近天線去完成模擬信號的數字化,而且數字化后的信號要盡可能多地用軟件進行處理,實現各種功能和指標。軟件部分主要用DSP芯片來進行處理信號。根據軟件無線電的知識,可以使用內插來完成精確性時延部分的工作,但為了避免插值后數據量的大增,導致DSP處理的負荷量過重,之后就得考慮數據的抽取操作用以減少處理的數據量。在上部分中,可以得出內插和抽取過程都需要一濾波器進行濾波,避免內插帶來的高頻鏡像和抽取帶來的頻譜混疊。可以采用內插和抽取組合的辦法來解決內插所導致的數據量大增問題,并保證小尺寸時延的精度。但必須內插在前,抽取在后,以確保其中間序列的基帶譜寬度不小于原始輸入序列譜或輸出序列譜的基帶頻譜寬度,否則將會引起信號失真。這里采取的是D倍內插再D倍抽取以實現級聯來滿足要求。但是由于他們級聯的D倍內插濾波器和D倍抽取濾波器工作在相同的采樣率Dfs下,所以他們可以以一個組合濾波器來代替。圖3是基于內插和抽取技術的時延器結構。

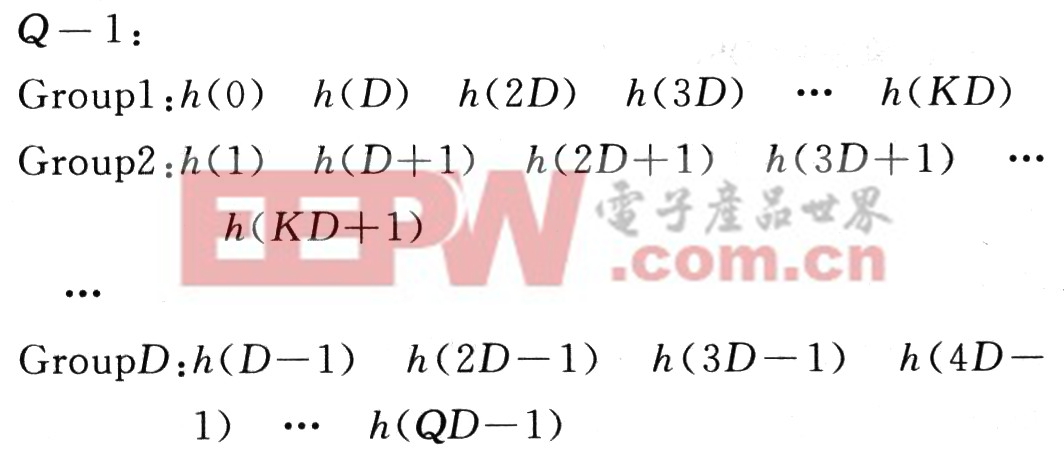

輸入信號x(n)的抽樣速率為fs,為實現延遲L/D個樣點間隔,首先將x(n)的抽樣速率增加到原來的D倍(即在x(n)的二個樣點間插入D-1個零),速率提高后的V(n)序列經低通濾波器濾波,低通濾波器的作用是濾除間隔為原抽樣頻率重復出現的成分。V(n)是x(n)內插后的序列,其抽樣速率為Dfs,u(n)在高抽樣率上延遲L個樣點后得ω(n),最后在ω(n)序列中,每D個樣點保留一個即得到y(n)。y(n)是x(n)延遲了(L/D)T的序列,這里T=1/fs是原序列的抽樣周期。在得出u(n)的過程中,經過的低通濾波器是FIR濾波器,V(n)序列經低通濾波器濾波時是利用![]() 產生的,但V(n)是通過x(n)的兩樣m=0點插零得到,也就是說在進行卷積運算時,將會有許多項是零乘以濾波系數的情況。根據規律可以得出,濾波系數每隔D個再相互與x(n)中相鄰數據相乘加得到。結合數字濾波器H(z)的多相濾波結構的知識,多相濾波器是由D個子濾波器構成的。各個子濾波器參數如下,其中N/D=Q,N為濾波器長度,Q為整數,令K=Q-1:

產生的,但V(n)是通過x(n)的兩樣m=0點插零得到,也就是說在進行卷積運算時,將會有許多項是零乘以濾波系數的情況。根據規律可以得出,濾波系數每隔D個再相互與x(n)中相鄰數據相乘加得到。結合數字濾波器H(z)的多相濾波結構的知識,多相濾波器是由D個子濾波器構成的。各個子濾波器參數如下,其中N/D=Q,N為濾波器長度,Q為整數,令K=Q-1:

在上面各子濾波器參數組中,相鄰濾波參數都相隔D個,也將是輸入信號x(n)依次通過各子濾波器后產生新的信號u(n),此時的抽樣周期TD=1/Dfs,即x(n)通過相鄰子濾波器后產生的輸出信號間的抽樣時間是一個抽樣周期1/Dfs。那么,x(n)依次通過子濾波器參數組中相距L相應的子濾波器時產生的輸出信號間抽樣時間是L/Dfs。這樣就能夠產生L個延遲樣點時間。最后再采取數據抽取工作。抽取工作其實可以采取對未被抽取的輸出信號相對應的數據進行內插濾波操作,而不對抽取的輸出信號相對應的數據進行內插濾波操作。這樣可讓DSP減少許多運算操作,節省DSP實現時延過程的執行時間,能夠保證信號數據的準確性。選用的DSP芯片是TI公司的TMS320C6416,主頻可以達到1 GHz,運算速度已達到8 000 MIPS,為32 b定點數字信號處理器。根據輸入信號x(n)的頻譜分析可得出最高頻率fmax(fmax≤fs/2),其中利用.Matlab或者SystemView軟件設計一個低通濾波器,得出濾波系數。

評論