自動反饋調節時鐘恢復電路設計

0 引言

信息技術的迅猛發展使得人們對數據傳輸交換的速度要求越來越高,因此,各種高速接口總線規范應運而生,從USBl.1到USB3.0,從PATA到SATA,從PCI總線到PCI―Express,其接口總線速度也由最初的Kbyte發展到現在的上G比特。在傳統的并行總線中,為了劃分字節,通常采用時鐘與多位數據并行傳輸的方式,這在當時數據率相對比較低的情況下,可以達到很好的效果,然而,隨著數據傳輸率的越來越高,這種并行傳輸的方式遇到了難以克服的困難。這是由于存在著時鐘畸變和路徑延時,使得到達接收端的數據位之間的數據與時鐘之間難以對齊,這樣,接收方就很難正確地接收數據。為此,在高速數據傳輸領域,串行總線越來越顯露出它的優勢來。高速串行總線多采用嵌入式時鐘來獲得上G的帶寬,并通過接收方的時鐘恢復電路從接收的數據里恢復出同步時鐘,實際應用中,通常有兩種方法:

第一種是時鐘數據恢復法,該方法是根據接收到的數據相位的變化來調整本地PLL或DLL電路的時鐘輸出相位,或根據本地時鐘相位來調整接收到的數據的相位的方法來達到數據與時鐘的同步,然后對數據進行l:1同步采樣;

第二種是過采樣技術,這種方法是在接收端用一個高速的時鐘對輸入數據進行過采樣,一般來說,這個高速時鐘的頻率是原發送端時鐘的3倍以上,這樣過采樣后的數據經過后繼的數據處理電路就可以去除冗余的比特,從而恢復出實際需要的比特信息。

這兩種方法各有優點和缺點,其中CDR方法由于不需要多倍于系統時鐘的采樣時鐘,因而系統功耗比較小,數字電路邏輯比較簡單,然而模擬模塊設計復雜,數據同步所需時間比較長。相對于CDR來說,過采樣技術數據恢復速度快,模擬電路設計簡單,但是,數據后繼處理電路相對復雜,功耗也較大。那么,有沒有什么方法可以綜合這兩種方法的優點呢?本文提出了一種新的高速串行數據恢復方法。

1 系統設計

1.1 系統總體電路

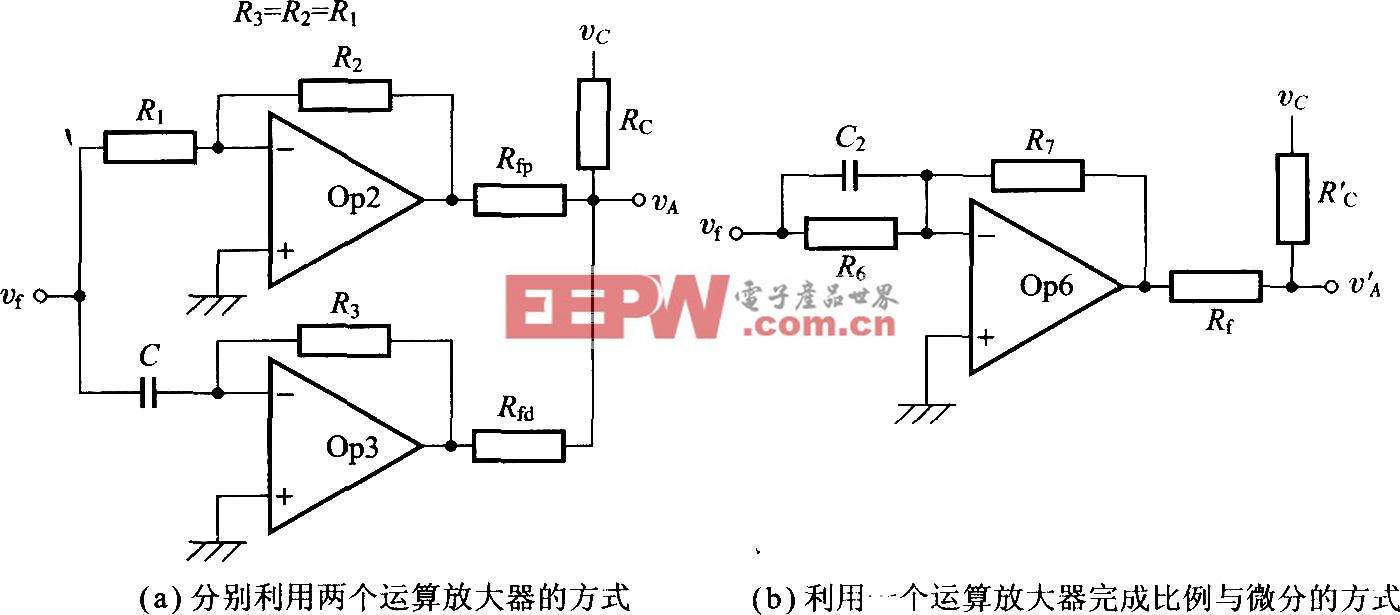

圖1是一種新型高速串行數據恢復電路框圖,此方法使用反饋通路來使本地時鐘能快速鎖定數據,該方法的抗干擾性尤其突出。

由于發生系統和接收系統的系統時鐘間存在著誤差,再加上傳輸通路上介質以及接收器本身的影響,使得信號的跳變沿存在嚴重的抖動和偏移,這樣,接收端就必然需要一個本地時鐘和異步數據同步的過程,本文采用的方法就是把輸入信號通過PLL鎖定延時器件的時延特性,將數據分為三路,每一路比上一路延時四分之一個時鐘周期,然后使此三路信號分別被本地時鐘采樣并比較,以從中得出中路信號與本地時鐘相位之間的延時是超前還是滯后,之后再將超前滯后信息經過譯碼邏輯變為一串8比特的控制信號給延時邏輯來調整時延,最終使數據與本地時鐘同步。

評論