基于FPGA-SPARTAN芯片的CCD的硬件驅動電路設計

3 驅動的實現及仿真結果

Max+PlusⅡ是Altera公司推出的一種開發設計平臺,他功能強大,可以生成文本文件和波形文件。并支持層次設計和從頂至底的設計方法,支持VHDL語言。可以編譯并形成各種能夠下載到各種FPGA器件的文件,還可以進行仿真以檢驗設計的可行性。

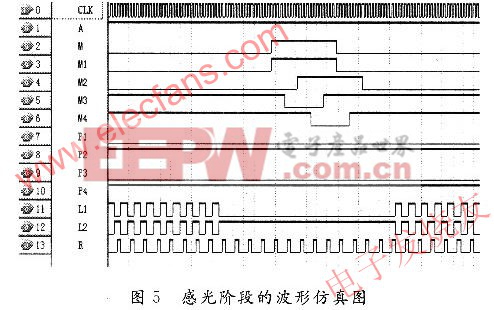

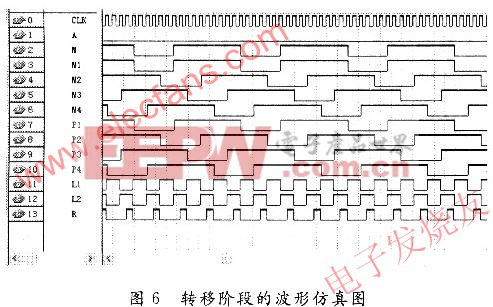

硬件描述語言(VHDL)是用來描述集成電路的結構和功能的標準語言,設計人員無需通過門級原理圖,而是針對設計目標進行功能描述,從而加快設計周期,VHDL元件的設計與工藝無關,方便工藝轉換。基于以上優點和上述的時序分析,該系統采用VHDL語言實現CCD驅動時序電路。由于系統的一次周期比較長大概在200 ms,所以波形仿真時的END TIME比較大,圖5所示為感光階段的波形仿真,圖6所示為轉移階段的波形仿真圖。

由圖可知設計所產生的波形與TH7888A的技術手冊上的驅動要求所需脈沖完全吻合,能夠達到TH7888A的驅動要求。

4 結語

用XILINX公司系列FPGA-SPARTAN芯片,在QuartusⅡ5.0開發環境下采用VHDL語言輸入方法開發設計出了高分辨率全幀CCD TH7888A的驅動電路,能夠產生滿足TH7888A要求的驅動脈沖。與以往常采用的驅動方法相比其面積大大減小了,采用FPGA進行設計,簡化了CCD驅動電路的電路系統。整個設計編程完畢后進行仿真、時序驗證正確后再下載到器件中,然后進行電路的測試校驗直到達到預期效果。這樣的設計修改起來較為方便,只要修改程序即可,不需要像傳統的設計方法要更換器件修改設計電路等,實驗證明,把VHDL應用于CCD驅動電路的設計,可以滿足系統的高速性和電路的集成度等要求。

評論