基于FPGA的PCIE總線擴展卡的設計

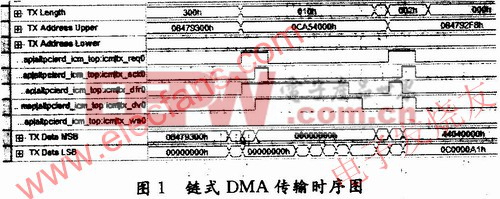

圖1是用SignalTap工具獲取的鏈式DMA讀時序圖。PCIE核接收tx_req0請求信號,然后給出一個tx_ack0,同時將tx_dr0置為有效,該信號套住的TXData就是需要讀取的有效數據。在每次DMA結束之后,PCIE核都會用同樣的控制邏輯給主機傳送1個已完成DMA次數的狀態字,如圖1中的44040000h。

4 性能測試

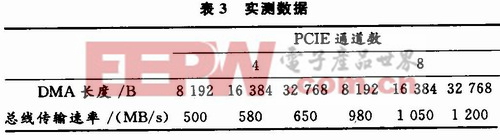

在做總線性能測試時,采用鏈式DMA傳輸方式,共4個描述符表。根據實際使用的PCIE總線通道數和DMA長度的不同,實際測試得到的總線速度也不同,表3給出了參考數據。

5 結語

使用FPGA來設計PCIE總線擴展卡,可以省去專用的PCIE接口芯片,降低了硬件設計成本,提高了硬件的集成度。利用FPGA的可編程特性,大大提高了設計靈活性、適應性和可擴展性。PCIE總線提供了高速、獨享的數據交換通道,確保在大數據量的數據交換時不會出現瓶頸,而且作為新一代總線,它使系統在獲得更高性能的同時,具有了良好的升級性。

評論