基于Xtensa可配置處理器技術的視頻加速引擎技術開發

4、自動化軟件開發工具套件支持

可配置和可擴展的關鍵是不僅能夠自動產生預先經過驗證的RTL代碼,用于設計人員定制處理器(包括所有系統擴展功能),而且還能夠自動產生完整的軟件工具,包括一個與處理器相匹配并經過優化的開發工具套件、一個基于時鐘周期的指令集仿真器以及系統模型。

這種自動化意味著編譯器知道設計人員所添加的新指令、相關的寄存器以及寄存器文件。因此,編譯器能夠對用戶定義的指令進行調度,并執行寄存器分配操作。類似地,軟件開發人員在調試時除了處理器本身的基本寄存器,還能夠了解設計人員定義的寄存器和寄存器文件;同時,軟件開發人員能夠利用指令集仿真器對設計人員定義的新指令進行仿真。與處理器相關的實時操作系統RTOS端口和系統模型也能夠自動產生。Tensilica的軟件工具能夠在一個小時內自動產生上述軟件工具,這是對使用可配置處理器用戶的核心承諾,能夠執行諸如SAD運算,而不必采用RTL那樣的實現方法。

5、采用可配置處理器構建視頻加速引擎建立多操作功能部件

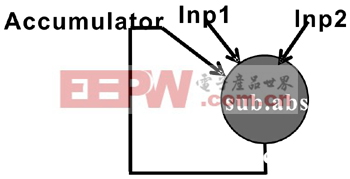

將SAD這樣的融合操作加到一個可配置處理器中是一件麻煩的事情。一條稱為“sub.abs.ac”的新指令可以完成“減法-絕對值-累加”運算操作。這條新指令能夠將圖2中的操作變成圖3中的復操作。

圖3 使用新指令計算“減法-絕對值-累加”操作

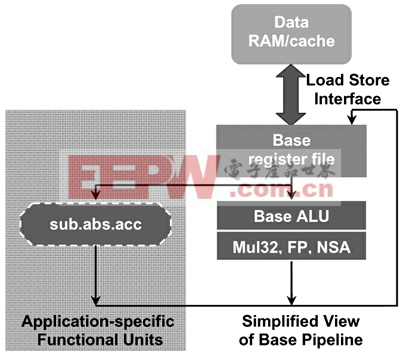

將該指令添加到處理器中后,C編譯器能夠識別這條新的“sub.abs.ac”指令,并調度相關指令;調度器將顯示“sub.abs.ac”功能部件所使用的內部信號;匯編器能夠處理這條新指令;指令集仿真器ISS能夠按照時鐘周期模式進行仿真。

新的專用視頻功能部件插入處理器后的數據通路簡圖如圖4所示。注意到,除了產生功能部件邏輯外,硬件生成工具還能夠自動插入前饋通路、控制邏輯以及旁路邏輯,以便將新的功能部件與數據通路中的其它邏輯互連。

圖4 插入sub.abs.ac視頻專用功能部件后的簡化數據通路示意圖

包含新指令的C代碼描述的SAD算法如下:

for (row = 0; row numrows; row++) {for (col = 0; col numcols; col++) {

sub.abs.ac( accum, macroblk1[row][col], macroblk2[row][col]);

} /* column loop */

} /* row loop */

正如前面提到的,對于一個16x16宏塊而言,增加新指令后程序主循環中的操作數減少到256個(即numrows = numcols = 16)。

評論