利用FPGA加密芯片的抗DPA攻擊電路設計

1.3 預充電技術的實現

普通邏輯門不能提供持續轉換活動,邏輯門的輸入不變將導致門的數據獨立。解決這個問題要通過增加預充電電路來提供變換。當時鐘為高時,連接預充電電路輸入一個預充電相位,連接點變化到邏輯O;當時鐘為低時,電路輸入計算相位,實際計算完成。在FPGA上采用預充電邏輯的目的是要求在預充電相位期間slice的輸出必須是邏輯O,有兩種方式來完成。在一個Xilinx的slice中,每個LUT后跟著專門的多路選擇器和內存單元,可配置為寄存器或鎖存器。這里考慮使用多路復用器和內存單元來實現預充電,每種方法各有優點和缺點:

(1)使用時鐘控制的多路復用器來實現預充電功能。將每個片子中單獨的內存單元作為寄存器,但是除了寄存器的普通時鐘還要分配一個反向時鐘。這種方法的缺點是復制一個時鐘信號并生成直接和互補信號將明顯增加功耗和電路面積,布線也將復雜化。

(2)使用內存單元作為帶有反向使能輸入的異步清零鎖存器來實現預充電功能。只需要一個單獨信號給寄存器和預充電鎖存器,預充電功能由連接反向使能輸入和鎖存器的清零輸入實現,使用這種方法的缺點是專門設計的寄存器存儲器需要一個單獨的slice。

2 DES加密模塊的實現

要在FPGA上實現安全防護結構來確保關鍵部件的功耗恒定。這里選擇從雙軌和預充電技術在FPGA上實現旁路安全防護邏輯。當前的技術水平需要在FPGA上進行精確控制布局和布線。下面從S盒硬件宏的實現和DES加密核的實現來介紹基于FPGA的DES加密模塊實現。

2.1 S盒硬件宏的實現

S盒的設計是DES算法關鍵部分,S盒設計的優劣將影響整個算法性能。在采用FPGA實現時,應從資源和速度的角度出發,有效利用FPGA可配置屬性,充分考慮器件內部結構,盡可能使兩者都達到最優。在設計中,由于綜合工具的介入,所輸出的網表很難被設計者所理解,同時要找到一種更好的方法來控制組合電路,因此要建立硬件宏模塊,簡稱硬宏。這與傳統的設計流程不同之處是要充分利用:FPG Editor的功能,目的是從FPGA底層結構的配置上實現雙軌和預充電技術。

通過Xilinx提供的FPGA Editor工具,首先讀入布局布線后輸出的NCD文件,并將其轉化為新的NVD文件,再送往BitGen軟件,進行布局布線的優化,最終在FPGA內部來建立目標電路,把它存為一個宏文件便于在上層進行調用。要注意兩個問題:建立硬宏需要進入到slice內部,準確控制Slice內部的器件選擇和器件之間的連線,防止設計出錯;宏的功能驗證要建立仿真模型,直接編寫一個行為仿真模型后在上層設計中調用這個仿真模型,要確保仿真模型和宏之間的一致性。

2.2 DES加密核的實現

DES算法的基本流程如下:首先,輸入明文通過初始置換,將其分成左、右各為32位的兩個部分,然后進行16輪完全相同的運算。經過16輪運算后,左、右半部分合并在一起經過一個末置換(初始置換的逆置換),于是整個算法結束。在每一輪運算中,密鑰位移位,然后再從密鑰的56位中選取48位。通過一個擴展置換,將數據的右半部分擴展為48位,并通過一個異或操作與一個48位密鑰結合,通過8個S盒將這48位替代成新的32位數據,再通過一級置換操作,這四步操作即為函數f。

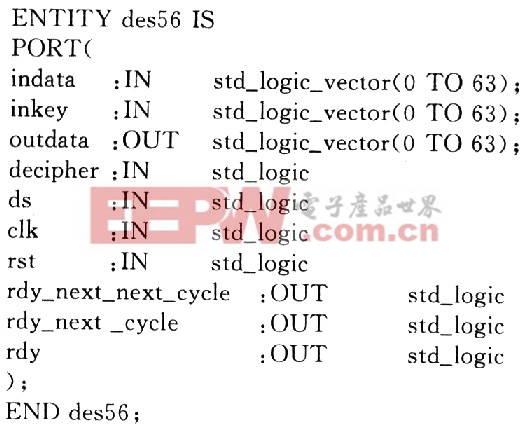

S盒是DES中的非線性模塊,直接決定DES算法的安全性。在函數f的實現中,采用上面的思路,使用例化調用了S盒。DES加密核的VHDL設計思路如下:首先調用庫函數構造ROM,然后使用VHDL語句進行行為描述。這種方法要結合器件的內部結構,對于小容量的ROM采用數組描述,大容量的ROM應采用元件的方式來實現。在VHDL設計中,庫函數、子程序的調用以及元件的調用和使用間接變量,都是影響速度的主要因素。由此得到DES Core的接口定義如下:

評論