可編程ASIC器件主從式結構開發系統的設計

1 引言

本文引用地址:http://www.j9360.com/article/151253.htm當前在EDA領域,只要具備臺式或筆記本電腦并裝有工具軟件,就可以方便地對可編程ASIC(CPLD/FPGA)進行設計開發,在系統可編程(ISP)器件為我們提供了這種便利條件。ISP方式雖然可以用一根下載電纜代替了編程器,但兼有提供下載和演示環境兩大功能的可編程ASIC開發系統對于用戶來說仍是必須的。本文提出的主從式下載開發系統可以適配多種目標芯片,具有較寬的開發應用范圍,經過幾年的教學、科研實踐,使用效果良好。

2 系統結構及工作原理

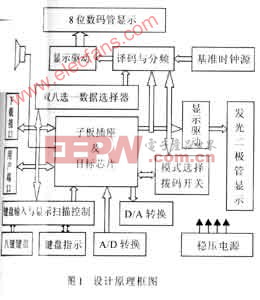

對ASIC器件設計開發的前期工作主要依靠對某種EDA工具軟件使用。對于其工具軟件和硬件編程語言,必須通過實踐鍛煉方能熟練使用和達到掌握技巧的程度。對應用系統和目標芯片進行開發,先要使用EDA工具軟件所提供的文本和圖形輸入方式進行描述和綜合,并要通過仿真驗證。而后的工作就是將設計完成并通過仿真的熔絲圖文件對目標芯片下載,并在系統板提供的開發環境中直接進行功能演示。因而下載開發系統的基本結構必須具備輸入和輸出功能。設計數字電路或系統往往需要多種頻率資源,故系統板要提供時鐘配置和頻率選擇功能。而要完成開發系統的復雜工作和模式選擇,系統控制功能也是必須的。基于以上思路設計開發的系統電路框圖如圖1所示。

|

本機最大的特點是系統采用主從式開發結構,將目標芯片安裝在一個小型轉接板上,再將轉接子板插到系統母板上配合工作。主系統母板是固定的,對不同的芯片只需換用不同的轉接子板,避免了以往開發系統只能對單一型號芯片進行開發應用的弊端,大大拓寬了目標芯片的可選性和開發系統的應用范圍。目前設計的開發系統適用于6000門規模的芯片開發,以及LATTICE、XILINX、ALTERA等多家公司的不同芯片。主從式開發結構保證了系統的通用性和易于升級,只要稍加改進就可形成從2000門到100000門以上邏輯資源、從5V 到3.3V、2.5V、1.8V兼容工作電壓的系列產品。

2.2 輸出部分

輸出部分主要采用數碼管顯示并有發光二極管顯示以及揚聲器發聲裝置。考慮到數碼管占用較多的用戶資源,我們采用一種動態掃描方式,在輸出數碼管顯示數據時同時輸出與該數據相對應的數碼管地址,經地址譯碼器形成數碼管選通信號。具體實現時用一片Isp LSI1016可編程器件配置數據選擇器和譯碼器,地址譯碼功能通過89C51單片機控制實現。這種方案大大節省了輸出口資源和譯碼驅動器件,提高系統可靠性同時減少印板空間。

設計系統具有三種顯示模式:準靜態顯示、十六進制碼輸入動態顯示和段碼輸入動態顯示,用戶通過撥碼開關或跳線進行模式選擇。

2.3 輸入部分

采用8鍵KEY 0~ KEY 7,鍵盤信號經89C51單片機處理后通過三態緩沖門送至用戶芯片,根據不同工作要求,鍵盤設計有四種輸入模式:琴鍵模式、乒乓模式、脈沖模式和二進制計數模式。除此之外第八鍵還可為特殊功能做單步時鐘輸入模式。

2.4 時鐘資源及分頻

使用ISPLSI1016同時配置時鐘產生單元,系統由晶振產生32768 Hz時鐘,經1016內部分頻可以輸出十種頻率,這十種頻率與另外單獨產生的12 MHz信號組合使用(分為四組),可基本滿足設計需要。對1016的ABEL-HDL語言描述(包括配置信號源部分的計數、分頻和顯示部分的譯碼器、數據選擇器)如下:

MODULEDIVCLK

TITLE ‘THIS IS THE HEX BITS COUNTER OF BIN BCD CODE TO 7 SEGMENT CODE CODER’

CK PIN 11; “Y0時鐘輸入”

EN PIN 15; “段碼輸入使能”

Q0,Q2,Q4,Q8,Q9,Q10,Q11,Q12,Q13,Q14,Q15 PIN 43,42,41,40,39,38,37,32,27,26,10

ISTYPE ‘COM’; “分頻器輸出”

NQ0,NQ2,NQ4,NQ8,NQ9,NQ10,NQ11,NQ12,NQ13, NQ14,NQ15 NODE ISTYPE ‘REG_D’;

C0,C1,C2,C3,C4,C5,C6 PIN 8,7,6,5,4,3,44 ISTYPE ‘COM’; “最終結果輸出”

A,B,C,D PIN 19,18,17,16; “十六進制碼輸入”

IN0,IN1,IN3,IN4,IN5,IN6 PIN 20,21,22,31,30,29,28;

“段碼輸入”

CLKIN NODE ISTYPE’COM’;

Q1,Q3,Q5,Q6,Q7 NODE ISTYPE’COM’;

NQ1,NQ3,NQ5,NQ6,NQ7 NODE ISTYPE ‘REG_D’;

QA,QB,QC,QD,QE,QF,QG NODE ISTYPE ‘COM’;

BOUNT=〔Q15..Q0〕; “分頻器輸出”

COUNT=〔NQ15..NQ0〕;

INPUT1=〔QA,QB,QC,QD,QE,QF,QG〕;

“譯碼結果輸出”

INPUT0=〔IN0..IN6〕; “段碼輸入”

OUTPUT0=〔C0..C6〕; “最終結果輸出”

分頻器相關文章:分頻器原理

評論