基于SPIFI外設的Cortex-M MCU嵌入式閃存選型解決方案

新型恩智浦ARM Cortex-M3微控制器首次采用的SPI閃存接口技術(SPIFI,已申請專利)可以幫助32位嵌入式系統設計人員以小尺寸、低成本的串行閃存替代大尺寸、高成本的并行閃存。利用SPIFI (讀音與spiffy諧音,意為“出色、整潔、漂亮”等——譯注),外部串行閃存可以映射到微控制器內存中,達到片上內存讀取效果。新技術可以解決傳統嵌入式系統外部閃存選型難題,為設計人員在保持系統性能的同時縮小尺寸及降低成本提供了一條新途徑。

本文引用地址:http://www.j9360.com/article/151175.htm目前恩智浦開發出一種新型外設接口技術,該技術在基于ARM Cortex-M3內核的最新LPC1800微控制器上已得到成功應用。嵌入式系統設計人員利用該技術可將串行閃存取代并行閃存,縮小封裝尺寸,降低系統成本。這種稱為SPI閃存接口(SPIFI)的技術目前已申請專利,通過該技術可將外部串行閃存映射到微控制器內存,實現片上內存讀取效果。SPIFI為設計人員提供了一種創新解決方案,在保持系統性能的同時達到簡化配置、縮小封裝體積、減少板載空間占用和節約系統成本的目的。

外部閃存的作用

采用32位微控制器(MCU)的嵌入式應用目前越來越復雜,需要完成多媒體、照片和其他各種數據密集型內容的管理任務。特別是人機接口系統,用戶現在都希望有圖形顯示,通過窗口、圖片、動畫、聲音和其他多媒體方式實現人機對話。此外,隨著市場的國際化,產品需要滿足多國語言要求,支持各種字母和字符。所有這些都對系統存儲資源提出了更高要求。

大部分32位微控制器都配有片上閃存,用于支持各種數據密集型功能,但是這種內存容量有限,通常無法滿足整體應用要求。片上閃存通常不足1Mb,雖然能夠解決主要應用代碼存儲,卻無法滿足其他應用資料的保存要求,比如:查找表單、圖像、照片、聲音文件、多國語言等。為此,設計人員通常要使用外部閃存。

與片上閃存相比,外部閃存成本要低很多,而且通常都有8Mb以上的現貨。使用外部閃存可以增加系統靈活性,系統運行時能夠更新升級軟件。

并行閃存與串行閃存的艱難選擇

對于外部閃存選型(串行和并行),設計人員通常要綜合評估,折衷考慮。并行閃存的速度通常比串行閃存快,但需要使用更多管腳、PCB布線和板載空間。

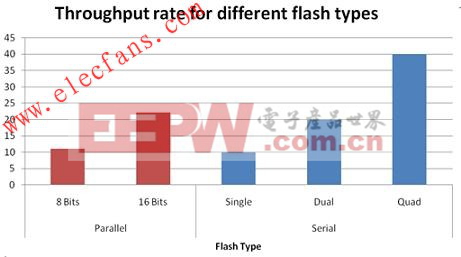

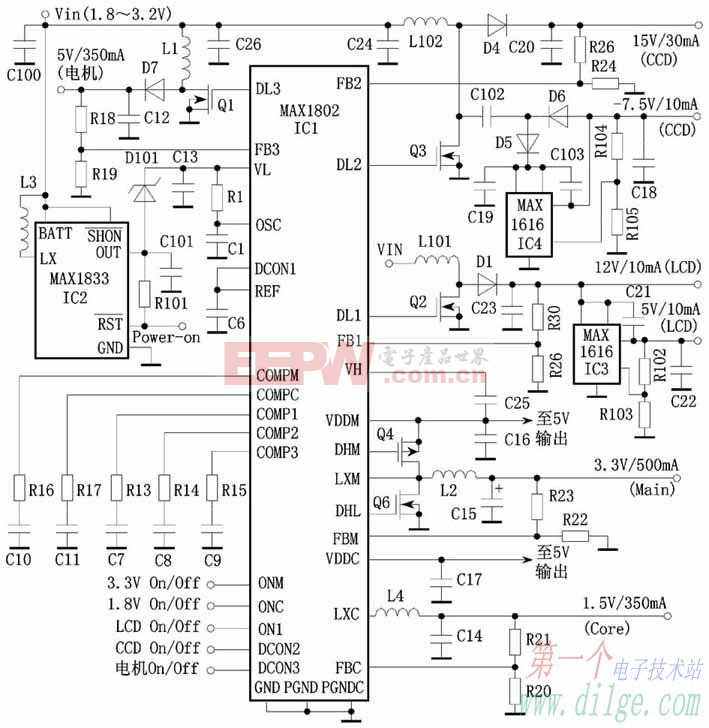

圖1給出了串行和并行閃存典型的數據傳輸速率。對于并行閃存,圖中假定無緩沖,固定存取時間為90ns。基于上述條件,16位并行閃存的最大傳輸速率22Mb/s。對于串行閃存,最大時鐘頻率80MHz的每位傳輸速率為80Mb/s,四通道串行閃存最大傳輸速率為40Mb/s。雖然該計算忽略了控制位,但四通道SPI閃存支持burst位,而SPIFI接口支持該功能,因此SPIFI接口可以達到上述傳輸速率。

圖1:串行和并行閃存的典型傳輸速率。

如圖1所示,典型的16位并行閃存每秒傳輸速率為20Mb。對于使用32位微控制器和32位外部閃存通信總線的系統(如恩智浦產品),設計人員可以選擇使用兩個16位并行閃存達到40Mb/s的傳輸速率。但是,增加速度的同時也會增加成本。這種配置使用兩個獨立的并行閃存,每個閃存有數十個封裝管腳,無論是封裝尺寸、管腳數量,還是PCB空間占用,都會遠遠超出設計人員的承受范圍。

串行閃存通常使用簡單的四針串行外設接口(SPI),從空間占用、功耗和成本等因素考慮是并行閃存的理想替代產品,但是傳輸速率非常低。通過圖1我們可以看到典型SPI閃存50MHz的傳輸速率僅為5Mb/s,而采用兩個16位并行閃存配置系統的傳輸速率是其8倍。另一個問題就是大多數微控制器SPI接口都與MCU外設矩陣連接,處理器訪問數據前必須先由驅動器代碼接收到內容并保存在板載RAM中。由于每次讀取串行閃存都要通過SPI軟件層,因此速度無法提高。對于采用標準SPI接口的外部閃存應用,速度可能無法滿足要求。

新型四通道SPI閃存采用改進的6針SPI配置,數據傳輸速率遠高于傳統的SPI接口。如圖1所示,四通道SPI每秒最大傳輸速率可達40Mb,與兩個16位并行閃存速度相當。由于減少了管腳數量和封裝尺寸,與并行方案相比,四通道SPI串行閃存可有效降低成本。雖然四通道SPI閃存完全可替代嵌入式系統中的并行閃存,但目前32位微控制器設計并不支持四通道SPI閃存的最大傳輸速率。這主要是因為四通道SPI接口與傳統的SPI接口連接方式相同,直接連接了微控制器外設矩陣。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論