面向ASIC和FPGA設計的多點綜合技術

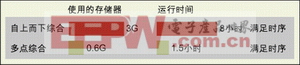

隨著設計復雜性增加,傳統的綜合方法面臨越來越大的挑戰。為此,Synplicity公司開發了同時適用于FPGA或 ASIC設計的多點綜合技術,它集成了“自上而下”與“自下而上”綜合方法的優勢,能提供高結果質量和高生產率,同時削減存儲器需求和運行時間。

本文引用地址:http://www.j9360.com/article/151084.htm盡管半導體技術在其發展過程中曾遭遇種種難以克服的障礙,但正如高登·摩爾多年前所預言的那樣,ASIC和FPGA的密度繼續每隔18個月翻一番。

硅潛力的疾速釋放是一件喜憂摻半的事。一方面,硅技術提供的功能與性能可以滿足最具挑戰性應用的需要;另一方面,當今設計工具的局限性令人沮喪,因為這使我們無法充分利用硅技術的全部潛力。隨著設計規模和器件復雜性不斷攀升,設計工作成為阻礙我們實現各類IC的制約因素。盡管電子設計自動化(EDA)行業近10年來一直致力于解決這個問題,但所謂的“生產力落差”仍在持續擴大。

設計綜合面臨的挑戰

這種生產力落差在綜合領域表現得最為明顯。傳統綜合方法的處理能力有限,因而要求將設計分割成不超過20萬門的子模塊。對于容量達2千萬門的芯片,設計者可能需要管理100個以上的不同子模塊,以完成一個設計的綜合。此外,大多數設計者更習慣基于功能或時序分割設計,相對而言,基于門數進行分割顯得不夠直觀。當前綜合流程的另一個缺陷是它們不能很好地優化分立的功能。這正是今天需要獨立數據路徑綜合的原因之一。嵌入式FPGA將既需要專門的綜合映射器,又需要在全芯片的背景下進行優化。

自十年前出現綜合技術以來,設計復雜性取得了驚人的增長。因此,傳統解決方案的效力正在衰退,這的確不足為奇。

設計復雜性還給綜合技術帶來許多其它問題。當一個綜合應用必須有效地操作大量設計數據時,存儲器利用率將變成一項真正的挑戰。除了龐大的設計規模外,處理計算任務所需的設計管理開銷也會使運行時間延長。隨著高復雜度、高約束性的功能被分解到綜合過程中,IP集成亦成為設計者必須面臨的另一項挑戰。為了不斷優化時序或理順子模塊之間的相關性,設計反復的次數將會大大增加,從而顯著延長設計時間。

在把綜合技術應用于復雜設計時,所面臨的另一個重要挑戰是保持設計穩定性。當把優化后的子模塊集成回整個設計中時,這可能帶來意想不到的復雜問題。隨著設計和硅技術變得越來越復雜,這些問題的復雜性將隨之增加。

為了克服綜合工具的上述缺點,設計者正在采用以下幾種策略。一種是復雜的外圍工作,如編寫高級腳本。這種基于外圍工作的解決方案雖然能夠達到目的,但通常會過度犧牲結果的質量(QoR)和生產效率。為了使用傳統方法成功地對一個大型ASIC設計進行綜合,這常常需要擴展的人工腳本,但由人工編寫腳本是極容易出錯的,而且要求設計者具有很高的腳本編寫技巧。這種方法只能給設計帶來很少的“增加值”,但卻要消耗寶貴的人力和時間。

另一個策略是專注于寄存器傳輸級(RTL)設計,然后將RTL交由ASIC供應商來綜合與實現。籍此,設計者可以避免與傳統綜合有關的麻煩。這種“RTL簽字確認(signoff)”方法非常依賴于高質量的RTL以及芯片供應商愿意為設計結果承擔風險的責任心。設計者可能會擔心設計被交付給那些對設計及系統問題知之甚少而且不關心設計能否成功的公司。

從這些策略的本性來看,它們假定綜合無法改進或者綜合就是瓶頸。然而,綜合是所有高級IC設計流程中一個根本的組成環節。無論由誰來執行綜合,只要這種技術繼續困擾芯片的實現,我們就會犧牲設計工作的生產效率和質量。因此,綜合是一個必須解決的重要問題。

“自上而下”與“自下而上”

傳統上,解決綜合問題有兩種方法:“自下而上”和“自上而下”。每種方法各有其長處和不足。“自下而上”的方法是指將設計分割成綜合工具處理容量之內的子模塊,從而使每個模塊能夠被獨立處理。這允許局部的重編譯和多處理,從而加速設計。“自下而上”流程還允許將設計的某個部分從整體中隔離出來,以進行改進。如果采用得當,這能提高結果的穩定性。

按單個模塊計算,“自下而上”法能提供最佳的運行時間,但整體運行時間可能因為項目管理和人工腳本開銷而有所延長。腳本編寫本身很重要,但也容易出錯。此外,這種方法可能會降低結果的質量(QoR)。采用“自下而上”法,綜合工具只能“看見”各個子模塊內的優化機會,而不能跨越分割界線對整體設計進行改進。分割的次數越多,設計離可能的最佳QoR就越遠。

“自上而下”的綜合方法考慮整個系統級RTL和約束,允許綜合工具在一次操作中優化設計,而不必跨越分割的模塊。與“自下而上”的設計相比,這種方法可產生最佳的QoR,因為綜合工具是在整個設計上進行操作。由于不需要人工腳本和管理各種不同的子模塊,它更易于實現。然而,它需要的存儲容量和運行時間使之無法應用于大型設計中。即使很小的設計改動也要求重新對整個設計進行綜合,這幾乎是不切實際的。類似地,“自上而下”法要對復制的模塊單獨進行綜合,與“自下而上”法對復制模塊一次綜合相比,這將導致更長的運行時間。最后,為了滿足時序要求,布局與布線過程將變得非常反復。從QoR方面來看,“自上而下”法是理想的解決方案,但從設計規模或其它設計要求來看,它并不是每種設計的最佳選擇。

多點綜合:面向大型設計的綜合技術

無論是單純的“自上而下”法還是單純的“自下而上”法都不是很多設計的正確解決之道。它們所需要的是集“自上而下”法的易用性及QoR優勢與“自下而上”法的高效率及低存儲器需求于一體的方法,而且這種方法仍要能夠被自上而下或自下而上地使用。這一點在大型設計中尤其重要,因為現有的“自上而下”或“自下而上”流程不能獲得最佳的QoR和運行時間。為了解決這個問題以及百萬門ASIC和可編程系統級芯片(PSoC)設計者所面臨的其它挑戰,Synplicity公司開發了多點(MultiPoint)綜合技術。

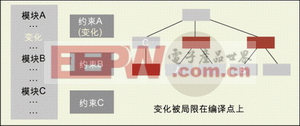

多點綜合技術針對大型設計而采用了一種分層方法。與傳統的“自下而上”分層設計不同,多點綜合技術能自動分割和優化設計。這是對整個設計執行語言編譯的結果,語言編譯能創建一種中間格式,它包含所有分層信息以及設計的關鍵信息。Synplicity公司的ASIC解決方案使用內置的HDL分析工具,允許用戶查看RTL設計分層或使用Tcl腳本來檢查設計分層。通過審視邏輯分層,設計者將選擇應該與其余設計部分分開綜合的分層單元。在分層結構中,這些點被稱為編譯點。

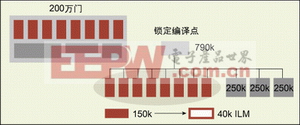

一旦選定編譯點后,時序約束將被施加到每一個點上;這個步驟最初將由人工執行,但未來可以自動完成。緊隨其后,將從編譯點開始對最低級別的設計層進行綜合。隨著每個編譯點被綜合,它會自動創建一個接口邏輯模型(ILM),并將其傳遞給下一個更高級別的設計層。最后,頂層是采用來自較低層編譯的ILM以及頂層的任何額外邏輯來實現綜合的。這能減少所需的時間,避免易出錯的腳本,從而使設計團隊可以將精力集中在設計的增值方面。

ILM是多點綜合所采用的一項關鍵技術。ILM是Synplicity或第三方公司為網表或綜合設計所編寫的部分網表。它們是包含所有邊界信息或時序分析邏輯的模型,因此能提供可與“自上而下”流程相媲美的QoR。由于ILM只包含從端口到寄存器的邏輯,而所有其它邏輯都被當成一個“黑箱子”來處理,因此它們大大降低了對存儲器的需求,并減少了大型設計綜合的運行時間。

用戶自定義的編譯點是創建ILM的基礎,而且是多點綜合技術的另一個關鍵要素。編譯點是能夠被獨立綜合的模塊,然后綜合的結果被用來綜合其上級模塊或頂層設計。多點綜合與其它綜合技術的一個關鍵區別在于,它能夠通過三類不同的編譯點(即軟、硬和鎖定編譯點)來控制邊界優化的層次。軟編譯點用于完全的邊界優化,這意味著端口標識可以在綜合期間改變。相反,端口完整性是由硬編譯點保持的。對于鎖定編譯點,模塊內的邏輯在優化期間能保持不變。因此,用戶自定義的編譯點可以充當綜合工具的指令,以便對設計的某一特定部分進行建模和綜合。由于允許跨邊界的優化,這些編譯點使 “自上而下” 的流程可以提供極佳的QoR。

多點綜合技術正是通過用戶自定義的編譯點和ILM來支持IP集成。它能自動對IP建模,并利用綜合的時序信息。在設計中充當范例的IP既可以在IP模塊內又可以在相鄰模塊中進行邏輯優化,同時不會影響內核自身的端口安排。

評論