簡析信號鏈基礎的時鐘抖動問題

引言

本文引用地址:http://www.j9360.com/article/150708.htm用于在更遠距離對日益增長的海量數據進行傳輸的一些標準不斷出現。來自各行業的工程師們組成了各種委員會和標準機構,根據其開發標準的目標(數據吞吐量和通信距離)確定抖動預算;同時還要考慮到組成通信鏈路的模塊的局限性。本文介紹時鐘抖動對高速鏈路性能的影響。我們將重點介紹抖動預算基礎。

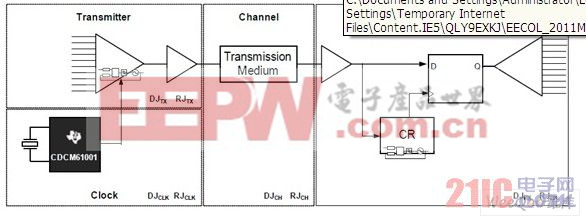

圖1:通信鏈路—抖動組件

圖1顯示了集成有一個嵌入式時鐘的典型高速通信鏈路。每個子系統(時鐘、發送器、通道和接收機)都會對整體抖動預算的增加產生影響。子系統抖動包括一個決定性(DJ)組件和一個隨機組件(RJ),如圖1所示。為了實現可接受的通信效果,必須滿足下列條件:

1 方程式1

其中:TJSYS是總抖動,而1UI為1個單位時間間隔(1比特時間)

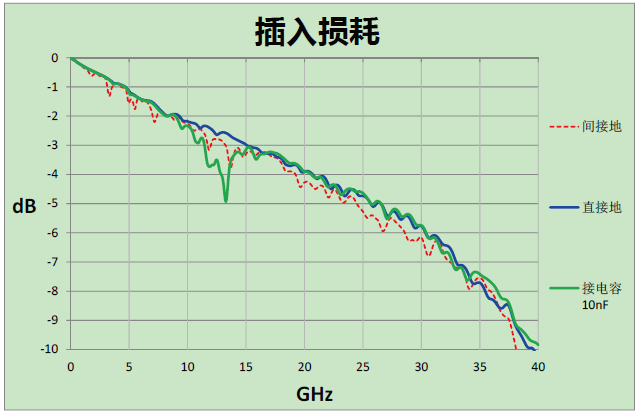

總抖動(TJ)包括每個子系統決定性抖動和隨機抖動的和。由于隨機抖動自身的屬性,進行這種求和時需要特別注意。隨機抖動呈現高斯(隨機)分布,并且無邊界。因此,隨機抖動可表示為一個RMS值,并且在規定測量/整合帶寬范圍內對其進行估算。例如,圖1所示接收機的抖動測量帶寬便為f2 - f1(參見圖 2)。這是因為接收機鎖相環路(PLL)追蹤 f1 以下的抖動(從而排斥它),而發射PLL的頻率上限為f2。從接收機的角度來看,使鏈路性能降低的隨機抖動降至這些限制之間。

圖 2高速通信鏈路—隨機抖動測量帶寬

評論