松耦合式可編程復雜SoC的設計實現

隨著科技的發展,信號處理系統不僅要求多功能、高性能,而且要求信號處理系統的開發、生產周期短,可編程式專用處理器無疑是實現此目的的最好途徑。可編程專用處理器可分為松耦合式(協處理器方式,即MCU+協處理器)和緊耦合式(專用指令方式,即ASIP),前者較后者易于實現,應用較廣。本文就是介紹一款松耦合式可編程專用復雜SoC設計實現,選用LEON3處理器作為MCU,Speed處理器作為CoProcessor。

本文引用地址:http://www.j9360.com/article/150604.htmLEON3及Speed

LEON3是由歐洲航天總局旗下的Gaisler Research開發、維護,目的是擺脫歐空局對美國航天級處理器的依賴。目前LEON3有三個版本(如表1),其中LEON3FT(LEON3 Fault-tolerant)只有歐空局內部成員可以使用。LEON3 (basic version)是遵循GNC GPL License的開源處理器,和SPARC V8兼容,采用7級Pipeline,硬件實現乘法、除法和乘累加功能,詳細特性請參考相關技術文檔[1]。

表1 LEON3的不同版本

目前,LEON3處理器因為開源、高性能、采用AMBA總線易擴展及軟件工具完備等因素,在國內外大學(如UCB、UCLA、Princeton University等)及科研院所的科研活動中得到廣泛應用。

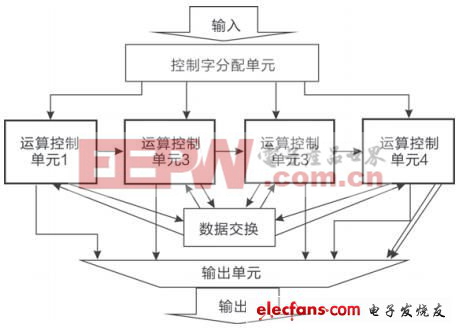

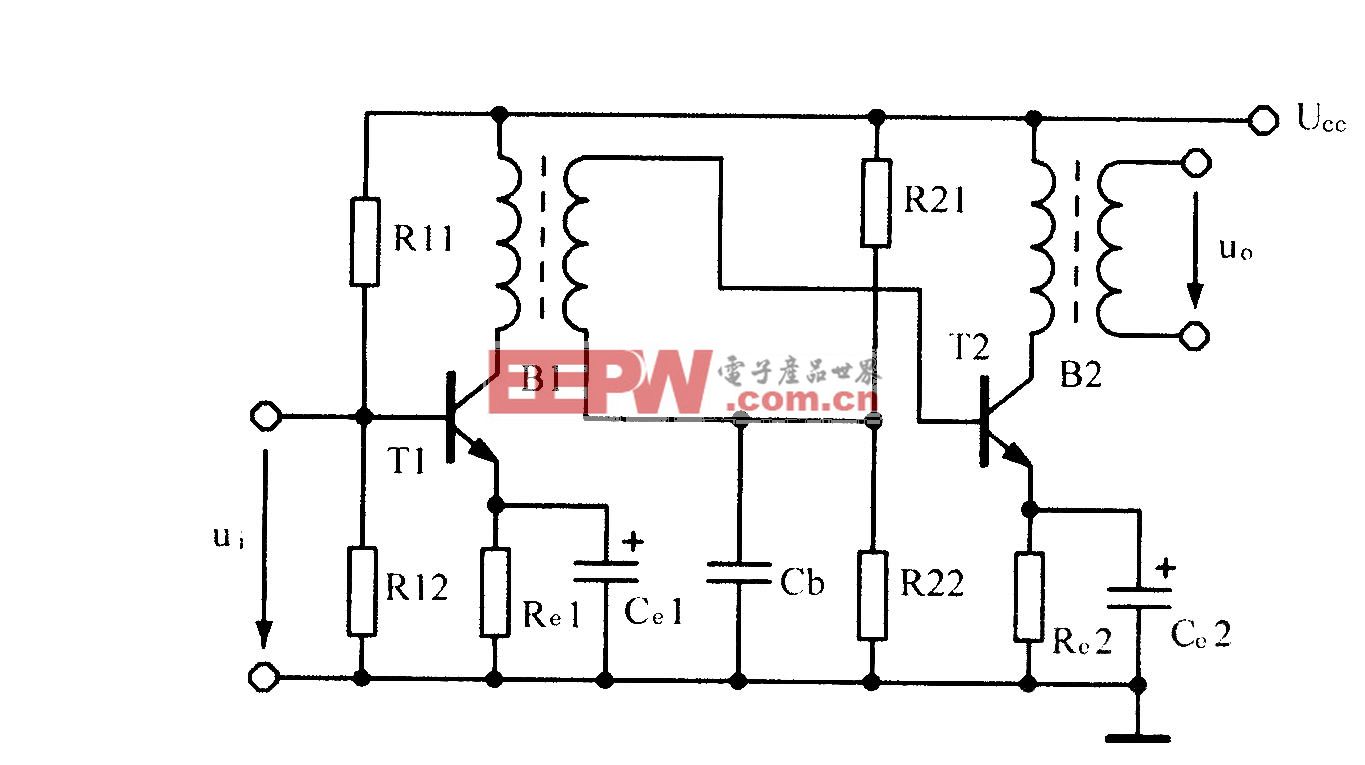

Speed(又名GA3816)是一款我國自主研發、處于同時代國際先進水平、可重構、可擴展的面向FFT、IFFT、FIR及匹配濾波應用的信號處理器,其內部結構如圖1所示,具有以下特點[2~4]:

1)Speed在追求運算速度的同時兼顧通用性,通過設置64位控制字,器件內部資源可根據不同應用進行重組;

2)可以實現FFT、IFFT、FFT-IFFT、FIR、滑窗卷積等運算,峰值運算能力達256億次浮點乘累加/秒;3)由160個實數浮點乘法累加運算器組成40個復數乘法累加器陣列,1Mbit的雙口SRAM,8個512×32bit系數ROM,兩個直角到極坐標轉換電路,兩個對數變換電路及其它輔助電路和控制電路。

圖1 Speed的內部模塊結構

Speed傳統的工作方式是通過片外FPGA輸入控制信號和待處理數據,這不僅增大了PCB板級布線、調試的工作量,而且FPGA不能用C等高級語言編程,算法改動起來不靈活。另一方面,隨著半導體工藝、微電子技術的發展,大規模的復雜SoC實現技術逐漸成熟,因此有必要將板級FPGA + Speed改進為芯片級MCU + Speed,這樣既能實現真正的可編程增大靈活性,又能加快用戶開發信號處理系統的速度。利用AHB實現通信

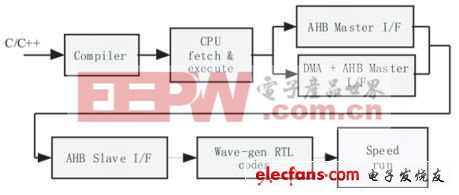

為了實現可編程,需要將C/C++程序表達的信息經過編譯器、LEON3處理器、AHB總線、DMA控制器和必要的HDL代碼,轉化成Speed能夠識別的信息,進入Speed模塊中,如圖2。其中AHB總線是LEON3 Core和Speed Core結合的關鍵。

圖2 實現軟件可編程的過程

評論