圖像的二維提升小波變換的FPGA實現

在提升算法的實現中,它的系數分布存在的特點,可以簡化設計的實現。

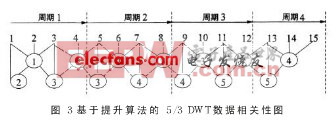

(1)對輸入數據的處理,只牽涉到了兩兩相鄰的數據(圓圈中的數字表示執(zhí)行的時鐘序號),數據相關性圖如圖3所示。對圖像數據進行行/列變換時,只需要得到該數據以及同一行(列)的相鄰兩個數據,就可以進行當前數據的行/列變換,而與其他數據無關,其本質是將奇序列數據與偶序列數據順次逐一輸入。因此,對數據輸入部分的處理可以通過構建兩個地址生成模塊,實現對奇偶地址數據的讀取。

(2)提升算法具有原位計算的特點,因此計算的系數可以直接替代原始數據而不需要附加數據存儲空間。對于它的行、列變換都可以只使用同一個存儲器RAM進行原始數據、中間數據和變換后數據的存儲。由圖4可以清楚地看到,二維提升小波變換后的系數在存儲空間的分布情況。原位存儲的特點大大地節(jié)省了片上資源,最有效地提高了系統(tǒng)利用率。

(3)行方向與列方向的提升小波變換是一樣的,因此可以將一維提升小波變換設計成一個獨立的模塊,之后對它進行反復調用。這也是簡化系統(tǒng)的有效途徑之一。

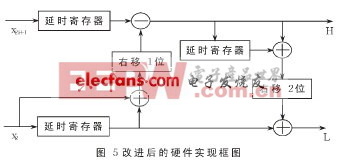

一維小波變換是二維小波變換的前提,對于它的FPGA實現,由圖2可以看出,5/3提升小波變換中主要計算是加、減運算,而除法運算是除以2和除以4,這在硬件實現中可通過“右移”操作實現快速運算。因此在設計中只需將圖2中的乘法器模塊用相應的移位操作模塊代替。而圖2中乘以-1/2模塊被替代為右移1位模塊之后,便少了一個負號,因此再將此乘法器后面的加法器模塊改為減法器,同樣達到了乘以-1/2的效果。這樣的改進還簡化了負數在硬件電路中的運算。改進后的硬件實現框圖如圖5所示。

二維小波變換的硬件原理結構如圖6所示,其工作原理如下:采用RAM1功能模塊來實現圖像數據的存儲;通過地址生成模塊來實現對存儲器中奇偶地址數據的分裂操作,先進行行方向的奇偶序列地址分裂,并做一維小波變換;行方向的操作一結束,立即進行列方向的奇偶序列地址分裂,并做一維小波變換。以上兩步反復進行,便可完成圖像的多級二維小波變換,最終的小波變換系數將被存儲在RAM2中。

4 二維5/3提升小波變換的FPGA實現

4.1 主要功能模塊的設計

(1)RAM模塊。要實現對同一個數據塊的雙輸出,以便進行一維提升小波變換,因此選擇了具備雙端口功能的宏模塊,用來存儲行小波變換系數和存儲列小波變換系數,這樣的結構能更加清晰地反映算法的實現流程,能夠實現算法中對奇偶地址數據的同時讀取。

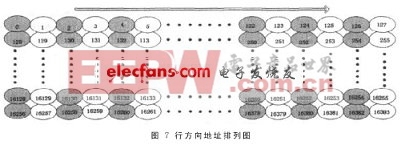

(2)行方向奇地址發(fā)生模塊和行方向偶地址發(fā)生模塊。行方向奇地址發(fā)生模塊實現功能是在每個時鐘周期內,依次輸出如圖7所示的白色圓圈所示存儲器行方向奇數單元的地址,這實際上是一個計數功能。行方向偶地址發(fā)生模塊實現的功能與行方向奇地址發(fā)生模塊類似,不同的是在每個時鐘周期內按行輸出圖7所示的灰色圓圈的序號。

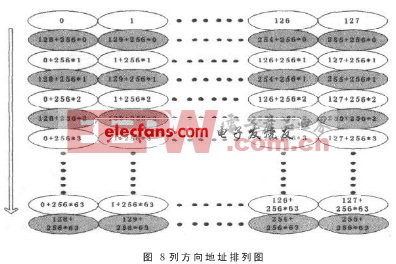

(3)列方向奇地址發(fā)生模塊和列方向偶地址發(fā)生模塊。在計數結束時,列方向奇地址發(fā)生模塊在每個時鐘周期內依次輸出如圖8所示的白色圓圈所示的存儲器列方向奇數單元的地址。列方向偶地址發(fā)生模塊實現的功能與列方向奇地址發(fā)生模塊類似,不同的是在每個時鐘周期內按列輸出圖8所示的灰色圓圈的序號。

評論