同步隊列串行接口QSPI的應用

1 QSPI工作原理

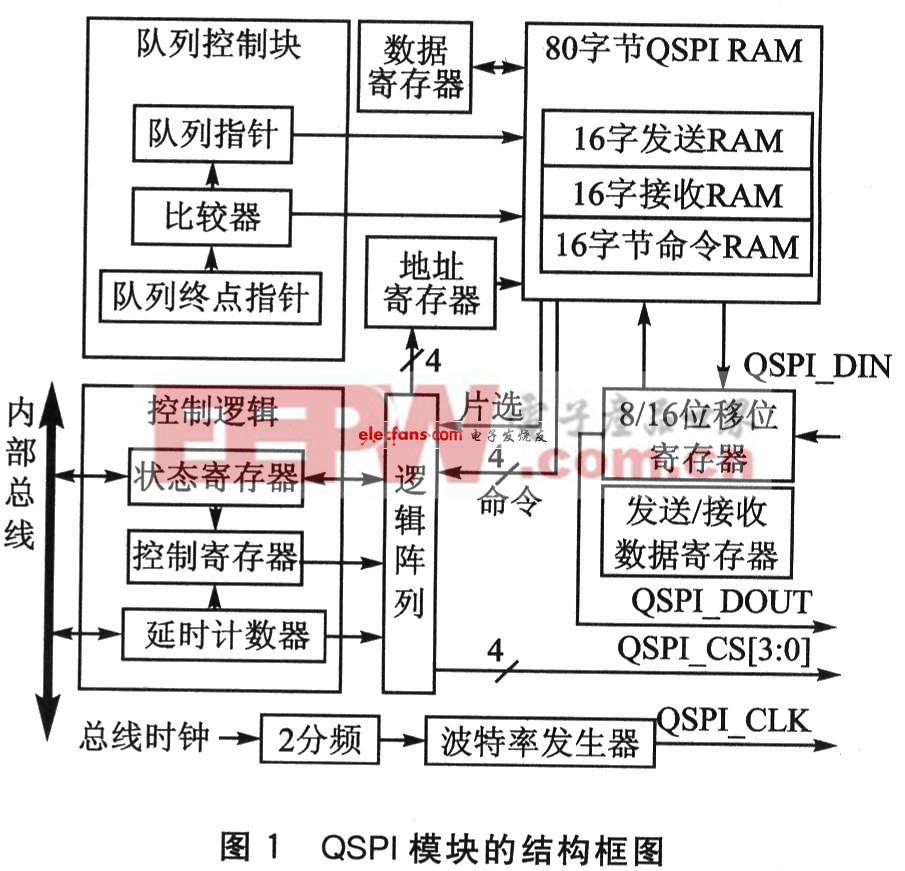

本文引用地址:http://www.j9360.com/article/150400.htm QSPI模塊的結構如圖1所示。與SPI相比,QSPI結構最大的特點是以80字節的RAM取代了SPI的發送和接收數據寄存器。80字節的RAM分成3部分:16字的發送RAM,16字的接收RAM和16字節的命令RAM。這3部分形成了具有16個QSPI傳輸控制組的傳輸隊列,每個QSPI傳輸控制組由1個命令RAM、1個發送RAM和1個接收RAM組成。每個QSPI傳輸的數據長度、片選等信息可由該QSPI傳輸控制組的命令RAM單獨決定。

由于SPl只有1個8位的發送數據寄存器,所以CPU每次最多只能準備一個字節的待發送數據。而QSPI擁有具有16個QSPI傳輸控制組的傳輸隊列,所以CPU每次最多可以準備16個待傳輸的數據,并且可以通過命令RAM設置每個待傳輸數據的長度。

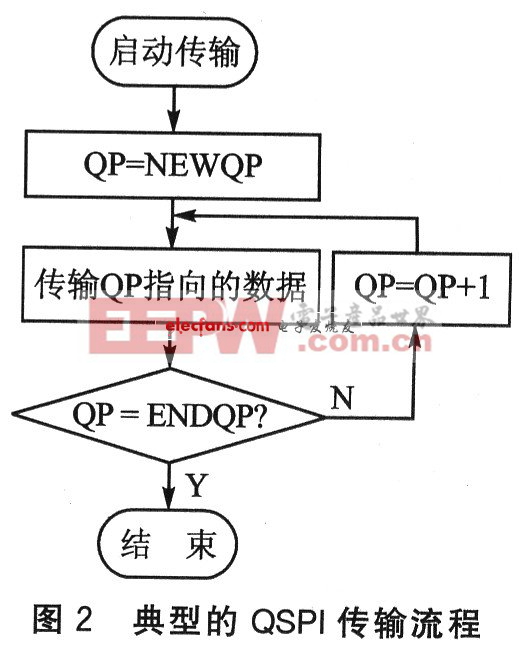

在QSPI模塊的QWR寄存器中,NEWQP和ENDQP域分別決定了傳輸隊列的起始點和結束點。起始點和結束點可以是16個QSPI

傳輸控制組的任意一個。當QSPI傳輸啟動時,QSPI模塊將從起始點開始依次發送準備好的數據直到結束點,整個過程無需CPU干預。典型的QSPI傳輸流程如圖2所示,其中QP為傳輸隊列指針,指向即將傳輸的數據。

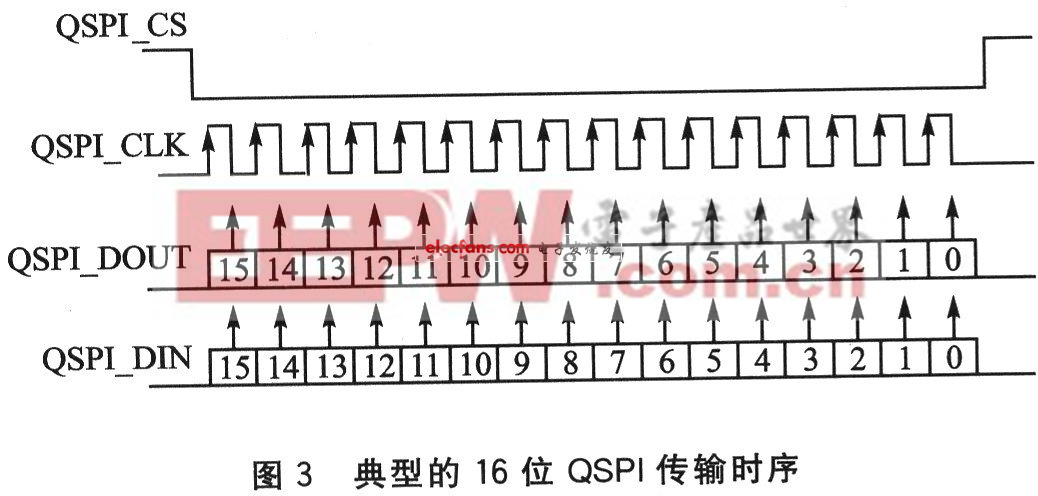

QSPI模塊具有7個引腳:QSPI_DIN為串行數據輸入引腳;QSPI_DOUT為串行數據輸出引腳;QSPI_CLK為串行時鐘輸出;QSPI_CS[3:0]為片選信號,通過外接譯碼器可以選擇多達16個設備。一次典型的16位QSPI傳輸時序如圖3所示。該時序假設片選信號低電平有效,時鐘空閑時為低電平,在時鐘的下降沿采樣串行數據。其中,時鐘空閑電平和采樣時鐘沿由QMR寄存器的CPOL和CPHA域決定。

評論