C5402 DMA結合MCBSP在數據采集系統中的應用

1前言

本文引用地址:http://www.j9360.com/article/150365.htm 在以C5402 DSP為核心組成的數據采集系統中,用戶一般需要在采集完一段數據后對其進行處理。采用查詢方式采集數據會占用大量CPU的資源,采用中斷方式來采集數據雖可以提高CPU的利用率,但是在采集數據的每個時刻還是由CPU來完成,同時降低了程序的可讀性。本文設計的數據采集系統利用C5402的存儲器直接存儲控制DMA與多通道緩沖串行口McBSP結合來設計系統,使得CPU正常工作與DMA數據采集并行進行,提高了DSP的運行效率。

2. C5402 DMA的特點

C5402存儲器直接存儲控制DMA能在不占用CPU資源的情況下,實現DSP存儲器間數據的自由傳送。C5402有6個可獨立編程的DMA通道,每個DMA通道受各自的5個16位寄存器控制:源地址寄存器DMSRC、目的地址寄存器DMDST、單元計數寄存器DMCTR、同步事件和幀計數寄存器DMSFC、發送模式控制寄存器DMMCR。

1. 源地址寄存器DMSRC規定DMA要傳送源數據的首地址。這些地址可以指向DSP內部存儲器、外部存儲器、片內外設和一些特殊的外部裝置。

2. 目的地址寄存器DMDST規定DMA要傳送數據目的地址的首地址。這些目的地址可以是DSP內部存儲器、外部存儲器、片內外設和一些特殊的外部裝置。

3. 單元計數寄存器DMCTR規定DMA傳送數據的個數為DMCTR寄存器的值加1個。

4. 同步事件和幀計數寄存器DMSFC規定DMA傳送數據的同步事件類型和傳送一塊數據所含幀信號的個數: DBLW位設置DMA工作在單字模式(=0b)或雙字模式(=1b)。工作在單字模式時每個數據單元設置為16位,雙字模式時每個數據單元設置為32位。 Frame Count位設置每塊數據所含幀信號的個數。 DSYN位設置選擇如下方式作為DMA同步事件: 0000b:無同步事件。 0001b:McBSP0接收事件(REVT0)。 0010b:McBSP0發送事件(XEVT0)。 0101b:McBSP1接收事件(REVT1)。 0110b:McBSP1發送事件(XEVT1)。 1101b:定時器0中斷事件。 1110b:外部中斷3(INT3)中斷事件。 1111b:定時器1中斷事件。 其它:保留。

5.傳輸模式控制寄存器DMMCR規定了DMA通道的傳輸模式: AUTOINIT位是DMA自動初始化設置位,可設置成自動初始化使能(=1b)和自動初始化不使能(=0b)。當DMA工作在自動初始化模式時,CPU在一個DMA事件完成后自動裝載下一個DMA初始化設置并繼續進行數據傳送。 DINM位和IMOD位設置DMA中斷產生方式。DINM=0時DMA中斷被屏蔽,當DINM=1時中斷按IMOD位設置產生。 CTMOD位設置發送計數模式控制,DMA可工作在多幀模式(=0b)和自動緩沖ABU模式(=1b)。 SIND位和DIND位用來設置源地址和目的地址的自動調整方式,可選擇如下方式:不調整(=000b)、訪問后自動加1(=001b)、訪問后自動減1(=010b)、訪問后按照單元地址索引寄存器DMIDX0的設置進行調整(=011b)、訪問后按照單元地址索引寄存器DMIDX1的設置進行調整(=100b)、訪問后按照單元地址索引寄存器DMIDX0和幀地址索引寄存器DMFRI0的設置進行調整(=101b)、訪問后按照單元地址索引寄存器DMIDX1和幀地址索引寄存器DMFRI1的設置進行調整(=110b)、保留(=111b)。 DMS位和DMD位用來選擇源數據和目的數據所存的空間,可選擇成程序空間(=00b)、數據空間(=01b)、I/O空間(=10b)或保留(11b)。此外,DMA的6個通道還受通道優先級和使能控制寄存器DMPREC控制。在這個寄存器中相應的DPRC位置1選擇相應的通道為高優先級,相應的DE位置1選通相應的通道為使能通道并開始工作。

3. 接口設計

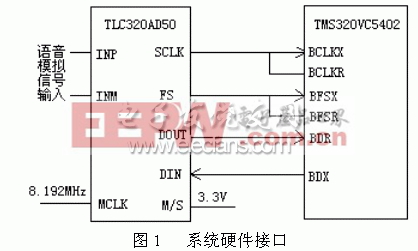

在這個系統中,使用的A/D數據轉換芯片是語音信號編碼解碼芯片TLC320AD50。它是TI公司生產的一個16位、音頻范圍、內含抗混疊濾波器和重構濾波器的串行模擬接口芯片。它完成語音信號的數字化采樣,并將轉換完的數據傳給DSP進行后續處理。

C5402提供兩個高速、全雙工、多通道緩沖串行口McBSP。它依靠三個信號實現發送數據和接收數據:數據線D(R/X)、幀同步線FS(R/X)和移位時鐘線CLK(R/X)。DX和DR引腳完成與外部設備進行通信時數據的發送和接收,由CLKX、CLKR、FSX、FSR實現時鐘和幀同步的控制。發送數據時,CPU將要發送的數據寫到發送數據寄存器DXR,在FSX和CLKX作用下,由DX引腳輸出。接收數據時,來自DR引腳的數據在FSR和CLKR作用下,從數據寄存器DRR中讀出數據。CLKX、CLKR、FSX、FSR既可以由內部采樣率發生器產生,也可以由外部設備驅動。設置DMA1通道與McBSP1通道結合來讀取TLC320AD50轉換完的數據。選擇McBSP1通道的接收寄存器DRR11(41h)為DMA傳送數據的首地址,并選擇源地址工作在訪問后不調整方式,選擇DMA通道同步事件McBSP1接收事件為DMA同步事件,來實現DMA和McBSP的結合。TLC320AD50轉換完的數據按McBSP1的設置被送到C5402內部接收寄存器DRR11中,再由DMA將DRR11中的數讀到指定數據存儲區來完成數據采集。DMA在傳送外部來的數據時不會影響CPU的正常運行,當DMA采集完一組規定個數的數據后產生一個DMA中斷事件中斷CPU,來通知CPU對其進行相應的處理,此時DMA可以按照設定繼續采集下一組數據,實現了數據采集與CPU處理的并行操作。

評論