Nios II實現二頻機抖陀螺工作電路設計

激光陀螺的工作原理是Sagnac效應,與傳統的機械陀螺相比,激光陀螺具有精度高、耐環境性能好、動態性能好、啟動時間短、壽命長及數字式輸出等特點,是捷聯式慣性導航系統的理想元件。

本文引用地址:http://www.j9360.com/article/150250.htm二頻機抖陀螺工作電路包括高壓電源、抖動驅動與噪聲注入、穩頻和信號解調等部分。系統設計以軟核處理器為核心.實時控制穩頻、抖動驅動與噪聲注入和高壓電源等單元,并實現陀螺讀取信號的鑒相解調與數字濾波。

Nios II是Altera開發的嵌入式軟核處理器,采用RISC精簡指令集,具有外設可定制、可裁剪性等優點,可方便嵌入Cvclone及Stratix系列 FPGA。陀螺信號處理系統中需要多種定制化的外設,而一般處理器無法滿足這種要求,因此NiosⅡ軟核處理器是處理激光陀螺陀螺信號的理想選擇。

2 系統結構設計

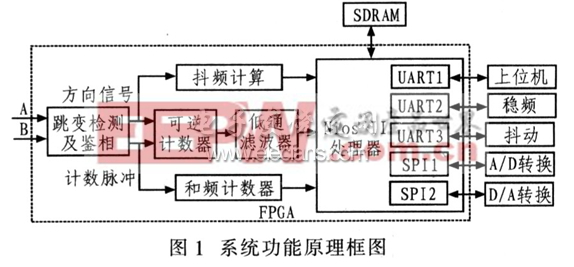

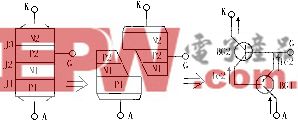

圖1為系統的功能原理框圖。圖中A、B為光電轉換器接收的拍頻信號過零比較后產生的方波信號,這兩路方波信號經跳變檢測和鑒相后產生跳變脈沖和方向信號。可逆計數器根據方向信號對脈沖進行可逆計數,而和頻計數器仍對脈沖進行正向計數。低通濾波器對可逆計數器的計數值進行濾波,并將濾波值輸入到處理器。UART1和上位機通訊,而UART2和UART3分別與穩頻和抖動電路通訊,以控制穩頻和抖動參數。2個SPI接口分別控制A/D轉換和D/A轉換的部分。

考慮到系統資源要求,FPGA采用Altera公司生產的EP2C200240C8,它屬于Cyclone II系列,其內部資源主要有:多達兩萬個邏輯處理單元(LE);52個M4K模塊,總共26 KB的片內RAM;26個18×18硬件乘法器;4個全局時鐘鎖相環;多達142個外部引腳。系統選用快速型Nios II處理器,處理器占用3 000多個邏輯處理單元,工作時鐘為100 MHz。由于系統處理器程序運行在SDRAM中,所以在構建系統時要添加SDRAM控制器,SDRAM使用HY57V283220,其存儲空間為16 M字節,完全能夠滿足處理器實際需求。處理器程序固件和FPGA的配置信息存儲在EPCS串行配置器件中,這樣可減少一片外置Flash。因為程序從 EPCS啟動,所以在SoPC設計時添加外設EPCS控制器以引導程序的初始運行。

3 信號濾波實現

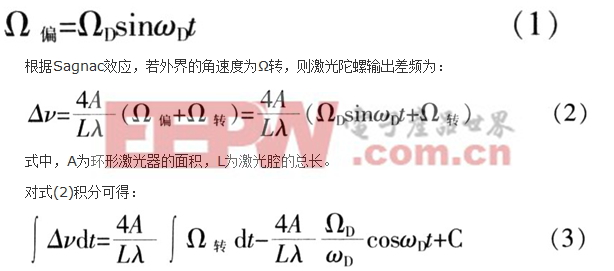

激光陀螺的讀取信號是由兩個光電管經光電轉換后產生的,工藝上要保證兩個光電管的拍頻相位相差90°,這樣便于在信號處理時進行相位檢測。為了盡量減小鎖區帶來的誤差,一般在陀螺中加入一個正負交變的正弦偏頻信號:

為了有效提取信號,通常是對可逆計數器的計數值(即式(3)的積分值)進行濾波。

評論