PCI9656實現與CPCI總線通信的雷達信號處理板

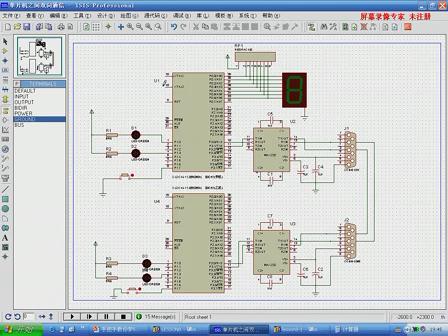

(1)PCI9656使LHOLD變高申請局部總線控制權;FPGA檢測到后,立即回應使LHOLDA變高告知PCI9656局部總線申請成功。PCI9656使ADS變低、LW/R變高,然后發送主機地址;FPGAl根據高位地址譯碼生成DSP片選信號,根據LW/R將主機接口配置為寫方式,同時使能PCI9656的READY。

(2)PCI9656檢測到READY后,將數據寫入雙口RAM。數據傳輸完畢后PCI9656使READY無效,收回LHOLD;FPGAl接著撤消LHOLDA。

(3)FPGAl向相應的DSP發出HBR和WRL申請總線控制權并請求對DSP寫數據操作,DSP檢測到信號返回HBG和ACK。FPGAl檢測到ACK信號后,開始將雙口RAM中的數據發送給DSP。數據傳輸完畢后FPGA使WRL無效,撤銷HBR;DSP接著撤銷HBG和ACK。此次寫操作完成。

4 結 語

提出的基于CPCI總線的高速通用雷達信號處理板設計,繼承了CPCI總線可靠、可擴展、通用性強的特點。PCI9656橋芯片和FPGAl邏輯轉換芯片實現板外主機對DSP的訪問。通過FPGA2將Rocket_IO口與DSP的LinkPort口互聯實現數據的高速傳輸。

評論