便攜式高速數據采集系統設計

2 AD1671控制及采集系統工作原理

圖3是AD1671的AD轉換時序圖。

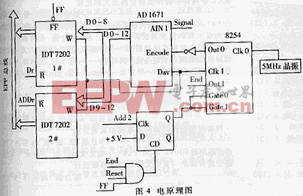

AD1671在Encode信號上升沿開始A/D轉換,Dav信號在本次轉換完成前一定時間變低,直到Dav出現上升沿表示本次轉換結束。為防止數字噪聲耦合帶來的誤差,Encode信號應在Dav信號變低后50ns內變低。系統中通過8254計數器對晶振進行分頻來給AD1671提供Encode信號,以滿足其工作時序的需要。系統原理圖如圖4所示。系統初始化時,向8254的Clock0寫入計數值,由此可以靈活改變采樣間隔,同時寫入Clock1的計數值用來控制采樣的個數。晶振采用5MHz有源四腳晶振,D觸發器實現觸發功能,系統工作原理如下:

AD1671在Encode信號上升沿開始A/D轉換,Dav信號在本次轉換完成前一定時間變低,直到Dav出現上升沿表示本次轉換結束。為防止數字噪聲耦合帶來的誤差,Encode信號應在Dav信號變低后50ns內變低。系統中通過8254計數器對晶振進行分頻來給AD1671提供Encode信號,以滿足其工作時序的需要。系統原理圖如圖4所示。系統初始化時,向8254的Clock0寫入計數值,由此可以靈活改變采樣間隔,同時寫入Clock1的計數值用來控制采樣的個數。晶振采用5MHz有源四腳晶振,D觸發器實現觸發功能,系統工作原理如下:

系統初始化完成后,經地址譯碼器產生Add2信號,使D觸發器狀態翻轉,由低變到高,8254計數使能端Gate0、Gate1變高,8254開始方式2的計數。當Clock0的計數時間到時,發出一個寬度為一時鐘周期的負脈沖,經反向送入Encode,啟動AD1671進行A/D轉換。一次轉換結束,利用Dav信號將轉換的數據寫入IDT7202,同時Clock1計數一次。當Clock1計數時間到后,發出一個脈沖,用來實現對D觸發器的清零,使Gate0、Gate1變低,停止AD1671轉換,完成一次系統的采集工作。

3 FIFO與EPP的接口電路

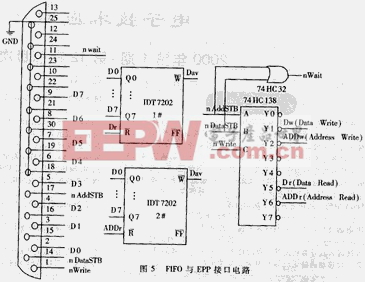

圖5是EPP與IDT7202的接口電路。

此電路是基于EPP1.9設計的。nDataSTB與nAddSTB組合產生nWait回送信號,實現連鎖握手。方案中分別用數據讀周期、地址讀周期對1#FIFO、2#FIFO進行讀取。EPP模式設定后,對FIFO存儲器的讀取非常簡單。通過產生一個單I/O讀指令到“基址+4”,EPP控制器就會產生所需的選通信號,用EPP數據讀周期傳送數據。對“基址+3”的I/O操作,可產生地址周期信號。

此電路是基于EPP1.9設計的。nDataSTB與nAddSTB組合產生nWait回送信號,實現連鎖握手。方案中分別用數據讀周期、地址讀周期對1#FIFO、2#FIFO進行讀取。EPP模式設定后,對FIFO存儲器的讀取非常簡單。通過產生一個單I/O讀指令到“基址+4”,EPP控制器就會產生所需的選通信號,用EPP數據讀周期傳送數據。對“基址+3”的I/O操作,可產生地址周期信號。

C語言指令如下:

讀一個字節數據:Data=Inportb(Base_Addr+4);

讀一個字節地址: Data=Inportb(Base_Addr+3);

實際應用中FIFO的存取時間達到ns 級,EPP的速度也接近ISA總線的速率。上述接口電路屬于高頻,電路設計要注意消除干擾。FIFO的讀寫信源應盡量靠近FIFO,沒用到的數據輸入端應接地或VCC等。

評論