基于32位CPU中Load Aligner模塊數據通道的設計與實現

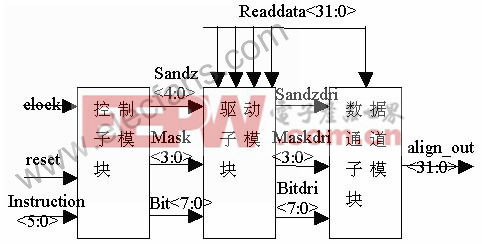

以上是Load Aligner模塊數據通道部分的設計。它還需要有控制模塊來產生上述控制信號,此外由于任何一個控制信號都要驅動數據通道子模塊中的32個cell,所以還要有一個驅動模塊來使控制信號有足夠的驅動能力。由以上分析,整個Load Aligner模塊的框圖如圖2所示。其中,控制模塊采用自動布局布線生成,而驅動模塊和數據通道模塊均采用全定制設計。本文引用地址:http://www.j9360.com/article/149270.htm

功能驗證

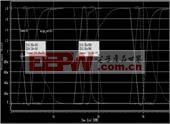

對此模塊的RTL代碼和所設計的電路分別進行了功能驗證。設從DCACHE取出的32位數據用十六進制表示為AABBCCDD,對表3中的所有指令進行測試。圖3所示的波形圖就是依次測試指令LW、LH00、LHU00、LH10、LHU10、LB00、LBU00、LB01、LBU01、LB10等的結果。可以看出,結果與表3完全吻合。說明所設計的電路滿足設計目標,可以實現所要求的所有指令。

電路仿真

根據圖1可以看出,從符號選擇信號Sandz4:0>到輸出的路徑為最長路徑,我們選取這條路徑進行仿真,并考慮在0.18μm時線電阻電容對時延的影響,用Hspice確定了所需器件的尺寸。仿真結果如圖4所示。上升時時延為0.52ns,下降時時延為0.47ns,均滿足小于0.7ns 的要求。

結論

在CPU中,Load Aligner模塊是DCACHE和數據通道之間的接口。從DCACHE中取出的數據只有通過Load Aligner模塊重新排序,才能進入CPU的數據通道。在設計中應用了自上而下的設計方法,所設計的電路實現了所有的指令,在時延上也達到了設計目標。

電子血壓計相關文章:電子血壓計原理

評論