采用ispPAC的濾波器設計步驟介紹

取b=k1k2,式(3)可以改寫成如下形式:本文引用地址:http://www.j9360.com/article/149155.htm

![]()

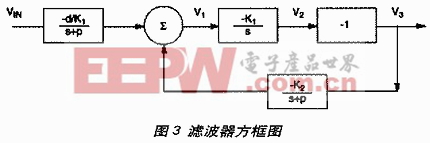

其等效的方框圖如圖3:

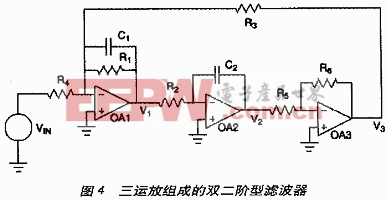

從方框圖中的函數中不難看出,系統可以分別用反向器電路、積分電路、有損積分電路來實現。把各個運算放大器電路代入圖3的方框圖中即可得到以下的實現電路,如圖4所示。

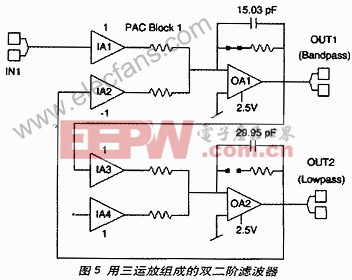

現在我們已不再需要利用電阻、電容、運放搭電路,然后才調試電路。現在完全可以利用系統內可編程器件方便地實現此電路。ispPAC10就能夠實現方框圖中的每一個功能塊,PAC塊可以對兩個信號進行求和或求差,k為可編程增益,電路中把k11、k12、k22設置成+1,把k21設置成-1。因此一個三運放的雙二階型函數電路可以用兩個PAC塊就能實現。在開發軟件PAC-Designer中使用原理圖輸入方式,把兩個PAC塊連接起來,電路如圖5所示。

電路中的CF是反饋電容值,Re是輸入運放的等待電阻,其值為250KΩ。兩個PAC塊的輸出分別為V01和V02。可以分別得到兩個表達式,即帶通函數表達式和低通函數表達式。

系統內可編程模擬電路的開發軟件PAC-Designer中含有一個宏單元,專門用于濾波器的設計,根據我們的設計要求算出對反饋電容,電阻和電路增益等參數,然后在電路圖編程環境下進行電路布線、修改其相應的參數值,系統的設計工作就基本完成。為了檢驗設計能否達到理想要求,開發軟件中還有一個模擬器仿真工具,用于濾波器的幅頻和相頻特性的仿真。如仿真的結果達到要求,則就可以通過下載電纜直接下載到ispPAC10器件中,整個設計工作完成。否則修改其參數,到仿真結果滿意為止。

結論

用ispPAC-Designer設計模擬濾波器極其方便,用一臺PC機就可以代替通常的示波器,掃頻儀和面包板,便工作效率得到很大提高,并且可以根據用戶的需要對系統作出調整而無須對PCB板作出任何改動,只須通過軟件在PC機中進行重新設計和性能仿真,然后下載到芯片中即可。整個工作在數小時內就能完成。

評論