Navigator Runtime 幫助您最大限度提高多內核效率

引言

本文引用地址:http://www.j9360.com/article/149132.htm多內核處理器給編程人員帶來了新的挑戰。在多內核項目中,半數以上的成本來自軟件開發。多內核編程的具體挑戰是非對稱多內核處理器 (AMP),因為其中相同的器件中駐留著 RISC 與 DSP 內核等不同類型的處理單元。這主要是因為操作系統 (OS) 對資源管理與負載均衡的支持非常薄弱甚至根本沒有,導致可擴展性差與資源利用率低。德州儀器 (TI) 創新型 KeyStone II 多內核架構提供專用硬件幫助實現調度與負載均衡功能,可簡化多內核可編程性。KeyStone II通過這些措施實現了多內核編程的性能突破。

AMP 編程挑戰

隨著多內核技術的演進,越來越多的 SoC 提供對稱多內核架構實現低成本以及更高的性能。典型的 AMP 具有運行在不同操作系統上的異構內核、硬件加速器以及非所有內核共享的分布式存儲器。在對稱多內核處理器 (SMP) 應用中,內核完全相同并運行支持相同共享存儲器架構的相同操作系統,因此使用操作系統帶來的內核間通信、調度以及負載均衡功能相對而言更為直接。AMP 器件的編程需要更高的并行編程技能,才能通過控制和協調不同的內核及操作系統實現可滿足單內核或 SMP 編程需求的高穩定性及高性能。

傳統非對稱多內核處理要求在編譯時對多內核資源進行靜態分區。這樣做難度往往較大,因為運行時的軟件加載不能提前判別,尤其是 4G LTE、LTE Advanced 以及云計算等尖端技術。一般解決辦法是預留額外的空間,以確保系統在最惡劣應用條件下也能正確運行。資源過度分配的不利影響是資源利用不足,最終會導致產品成本上升。另一方面,首次使用時或者引入新功能、需要現場強化或需求改更時,手動重新分區及軟件優化會帶來大量的軟件工作。

同步性及處理器間通信 (IPC) 的效率在多內核編程過程中至關重要。缺乏對各種同步性與 IPC 機制的適當硬件支持,會因過多的軟件開銷而導致多內核利用低下,降低系統性能。

這對 AMP 多內核系統而言尤為如此,因為難以實現軟件可擴展性與靈活性。

多內核導航器助力實現創新

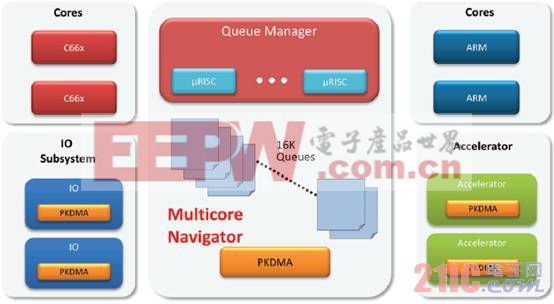

多內核導航器是一種基于數據包的創新基礎設施,支持數據傳輸與多內核控制。TI 異構 KeyStone 架構完美整合了 DSP Core-Pac、ARM® CorePac、硬件 AccelerationPac 以及 I/O 外設。它們不但可通過 TeraNet 進行物理互連,而且可通過多內核導航器進行邏輯互連。在 TI KeyStone II 架構中,多內核

導航器不但包含可容納 1.6 萬個硬件隊列的隊列管理器,通常存放指向各種數據包(由描述符及數據有效負載組成)的指針,而且還包含 8 個 3,200 MIPS uRISC、用于傳輸數據的數據包 DMA 以及支持 100 萬個描述符的硬件數據結構。此外,還可在 AccelerationPac 與 I/O 子系統中構建數據包 DMA,這樣多內核導航器無需內核干預,便可將數據從任何單元傳輸至任何端點。

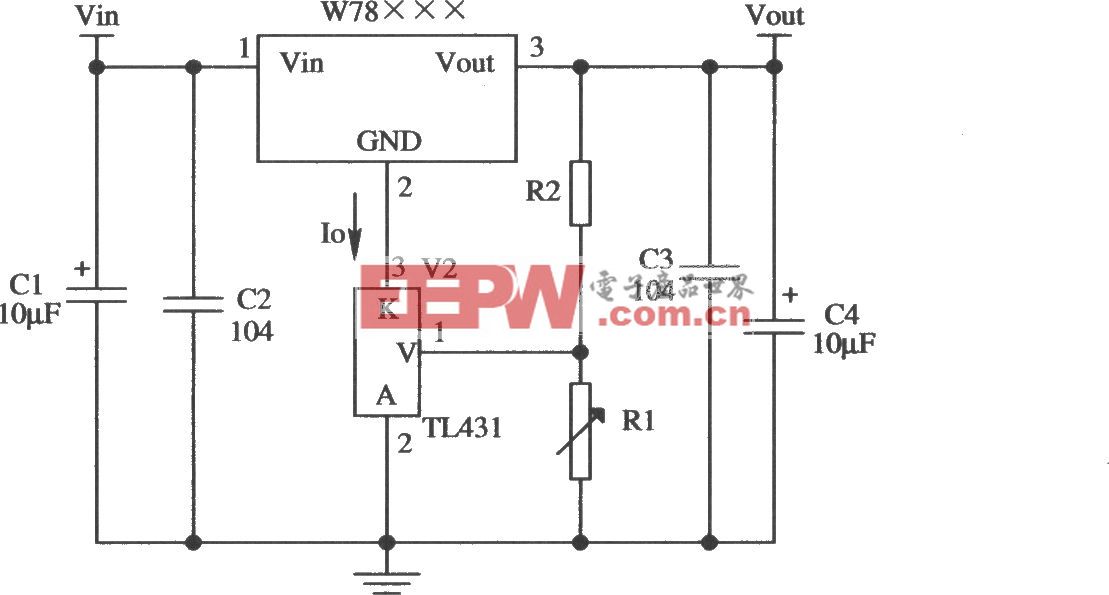

多內核導航器為 CorePac、AccelerationPac 以及 I/O 提供統一接口,可將硬件隊列用于圖 1 所示的不同系統端點。這可為所有 IP 塊提供支持通用通信方式的 AMP 系統。多內核導航器可充分利用內建在隊列管理器中的 uRISC 內核來管理流量路由、IPC、資源管理、調度以及負載均衡,從而可優化和加速數據流。各種任務可由隊列管理器按需派送和分配給負載最輕的內核或 IP 子系統。

圖 1:多內核導航器子系統

評論