基于DSP和CPLD的光纖陀螺信號采集系統設計

3 系統硬件結構

系統主要由DSP芯片TMS320F2812、雙口RAMCY7C131,CPLD芯片EPM7128T1100、ADC芯片ADS8364以及傳感器信號調理電路組成。

DSP主要負責與上位機通信,以及和CPLD共同控制AD實現對多路光纖陀螺數據的采集,這里選用TI公司生產的TMS320F2812。該芯片專門為控制系統應用而設計,它采用1.8 V的內核電壓,具有3.3 V的外圍接口電壓,片內存儲容量為18 KB SRAM,128 KB FLASH,最高主頻150 MHz,片內集成有多種外設接口。

雙口RAM主要輸出數據采集指令并接收DSP傳送的陀螺值。選用的雙端口RAM型號為CY7C131,采用5 V供電,容量為1K×8 b,實際使用數據交換區為256×8 b。在256 B的存儲空間內分為兩個數據區,一個數據區(A)存放上位機下發的指令信息,另一個數據區(B)存放采集的陀螺數據信息。由于控制DSP與上位機對雙口RAM的讀寫速度不同,為防止由于速度不匹配造成的讀寫沖突,在軟件中相應的存儲區設置讀寫標志位,通過此標志位來確定雙端口RAM的讀寫狀態。

在本系統中,CPLD是一個重要的組成部分,由CPLD組成的邏輯控制模塊接收DSP傳送過來的動作命令,控制AD某通道進行數據采集。這里選用Altera公司的EPM7128芯片。CPLD作為一個單獨的控制執行結構,通過編寫相應VHDL代碼,即可生成相應的操作電路,實現對各種輸入信號的鎖存、判斷和對控制信號的執行。

A/D轉換芯片選用TI公司的高速、低功耗、六通道同步采樣的16 b轉換器ADS8364,可保證采樣精度達到12位以上。芯片內部包含六個采樣保持器,可保證六路信號同時采樣;信號輸入范圍為0~5 V,最大轉換速度250K,可以滿足電位計、旋變信號采集速度和精度的要求。并且數字邏輯電平為3.3 V。考慮到數據采集處理系統的采樣頻率一般較高,如果用DSP直接控制ADS8364的訪問,將占用DSP較多的資源,同時對DSP的實時性要求也較高。因此在本系統設計中,用CPLD實現ADS8364的接口控制電路。

陀螺模擬信號是-5~+5 V差分信號,通過信號調理,轉化到0~5 V之間。當轉速低的時候,因受系統影響信號上有毛刺,需要進行濾波,設計一個RC低通濾波電路去掉高頻干擾即可。

4 系統軟件流程

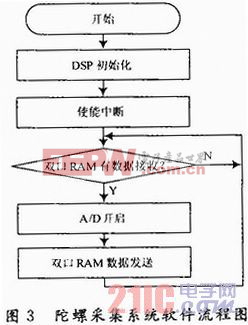

系統中DSP軟件代碼主要由兩部分組成:與上位機通信和對陀螺信號的采集。軟件開發在CCS3.1(Code Composer Studio)中進行。TMS 320F2812的主程序流程如圖3所示。本文引用地址:http://www.j9360.com/article/148954.htm

系統上電后,首先完成DSP中各個寄存器的初始化,包括配置RAM模塊,設置定時器、中斷等,然后系統進入循環等待狀態。進入中斷,首先對雙口RAM進行查詢,監測是否有采集指令下發,如果有,則啟動A/D,然后把數據通過雙口RAM傳給上位機,否則返回循環等待狀態。

評論