基于ISP技術的電子鐘設計

要求能啟動或停止電子鐘運行,且能在電子鐘停止運行狀態下修改時、分、秒的值,可增加一個啟動/停止控制端實現。如啟動/停止控制端接低電平,分頻模塊的時鐘接1 kHz的連續脈沖,其他模塊分別接對應輸出,電子鐘便啟動。而當啟動/停止控制端接高電平,分頻模塊的時鐘接地,其他模塊的時鐘分別接3個單脈沖手動輸入,電子鐘停止運行,手動產生一個單脈沖,與其相連的模塊就計數一次,達到了修改時、分、秒的目的,即實現了電子鐘更改時間的功能。本文引用地址:http://www.j9360.com/article/148925.htm

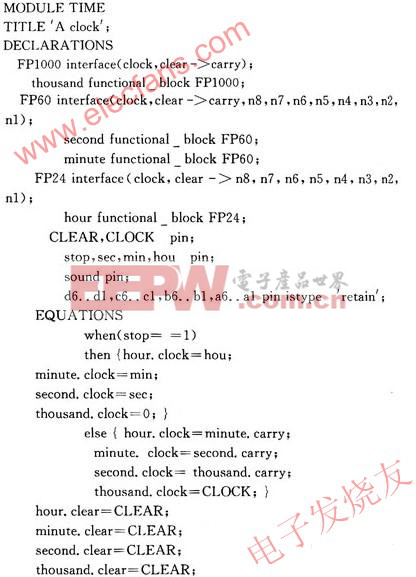

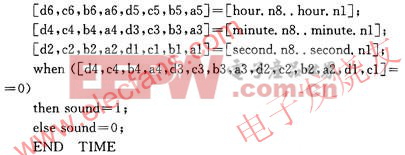

3.3 ABEL語言描述

下面用ABEL語言的層次結構實現電子鐘的設計可分為頂層模塊Clock,3個底層模塊FP1000,FP60和FP24。下面介紹頂層模塊CLOCK,其中調用了3個底層模塊。

4 結 語

從上例可知,用ISP器件可進行各種數字電路實驗,代替了古老的面模板實驗,而且靈活方便,是一種較理想的數字電路課程設計方法,值得推廣應用。

評論