對基于SoC系統設計的探查

調試復雜電子系統從來都不是一項簡單的工作,但至少是可以實現的。您要找到問題所在。采用您最相信的“示波器”,通過模擬電路到數字轉換,您可以追溯到問題的源頭。然后,編寫測試小程序,檢查驅動和外設,增加一些邏輯探針,再回到外設控制器和CPU總線上,最終解決問題。當然,這需要利用別人的一些代碼。

本文引用地址:http://www.j9360.com/article/148747.htm而芯片系統(SoC)集成從根本上改變了這一切。今天,微處理器、總線、外設控制器以及大部分存儲器和模擬電路都被包封在一個封裝中。它可以是ASSP、高級微控制器、FPGA,或者您自己設計的ASIC。不論SoC是什么,事實上是,除非芯片設計團隊愿意幫助您,否則,您不可能深入了解芯片內部。

在嵌入式CPU中調試硬件,為您提供斷點和準實時跟蹤等傳統調試功能,從而幫助您完成調試工作。但是,對于他們自己,調試內核也只是給出了您系統的CPU外觀視圖。如果不能針對系統總體狀態來更廣泛的定義某一事件,那么,當事件發生后,您可能需要編寫診斷短代碼,使系統暫時停止工作,將相應的數據寫回CPU。這一過程最好的情況是僅僅耗費了您的時間,而最差的情況是,耗費了時間卻不一定能解決問題,效率非常低。

硅片知識產權(IP)供應商提供越來越精細的SoC儀表調試手段,從而解決了這一難題。但是,當今的產品是個性化的,而不是標準化的。系統設計人員需要在芯片設計早期階段獨立作出選擇,而另一公司的其他團隊則根據產品能否及時面市、管芯面積等來確定自己的目標,并不關心能否方便的進行系統調試。而芯片設計人員、軟件開發人員和系統設計人員等參與者還是有一個共同點——互相協作,在系統級找到問題所在。

從一開始就做好規劃

實際上早已決定了您是否能夠成功的找到系統中的問題——兩年前,在您目前正在使用的SoC的開發階段。Brad Quinton是泰克公司嵌入式驗證的首席規劃師,他認為在芯片設計早期階段進行規劃非常關鍵,不僅僅是能夠充分探查芯片,而且還涉及到采用什么樣的調試硬件。然而,這并不常見。

芯片設計團隊的確在測試結構中開展了前端工作,但卻是出于其他原因。芯片中置入了測試設計和內置自測試硬件來支持IC測試。但是,這些資源并不是用于調試,一般只提供很少的診斷信息。芯片設計人員會專門針對硅片開發團隊而內置工具,但是,這些工具可能只有內部文檔,硅片一旦發布后,就會禁用這些工具。高速串行端口上會有邊界掃描,甚至是非常復雜的儀表功能,必須在系統中對其進行調整。但是,這些手段是為了在電路板級建立并驗證連接能力,而不是用于系統調試。

Quinton質疑,雖然這些結構非常有用,但是芯片設計人員會有更多的問題。Quinton認為,“從系統級進行考慮。關鍵接口、高級狀態機在哪里?通過掌握哪些信息您能夠知道哪一子系統正在工作?”

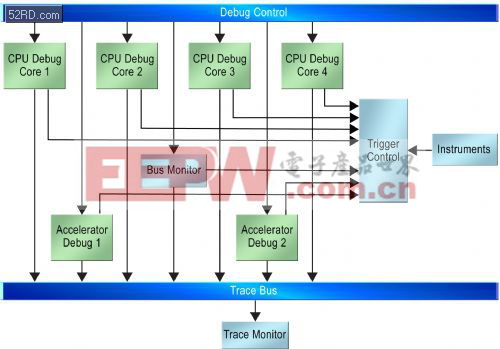

這些思考導致某些IP供應商開發了一類新模塊:在SoC中設計實現儀表和控制器,不僅供設計芯片的IC團隊使用,而且還有使用它的系統設計團隊,如圖1所示。

圖1.片內調試電路本身會成為實際的設計。

從不同的方向開始工作,兩類供應商驗證了這一發展趨勢。ARM擴展了其CPU內核調試內核CoreSight,涵蓋了多核SoC的大部分工作,而現在是泰克一部分的Quinton Veridae從儀表模塊開始,集中開發觸發器/蹤跡控制器,包括了CPU調試內核。這兩種方法對于系統調試人員都非常寶貴。這都為在SoC基礎上擴展可探查性提供了重要的理念。

數據源

雖然您想立即開始在系統結構圖中加入各種各樣的數據采集節點,而Quinton首先提出了一些基本問題。誰會使用調試功能:應用編程人員、模擬設計人員,還是機械工程師?他們會在哪一抽象等級上來定義事件;功能調用、信噪比、扭矩讀數?這些用戶會怎樣做:確定他們的代碼熱點、找到瞬變噪聲,或者知道驅動桿為什么失效?只有您理解了問題所在,才能夠找到解決問題的數據。

Quinton認為,現在的技巧是確定在哪里收集數據。很明顯,首先是在源頭采集所有數據:A/D轉換器(ADC)輸出、狀態寄存器、網絡接口等。當然,您希望盡可能獲得接近源頭的一些信息,例如,受控物理器件的狀態等。

但是,在其他情況下,事先考慮好在哪里采集數據可以減少測量開銷,以及后分析所需要的數據量。Quinton建議,“找到關鍵地方來觀察系統。在一點上所通過的系統狀態量會讓人感到驚訝:例如,CPU與系統總線的接口。”

在哪里對數據進行采樣也取決于用戶所希望的抽象級。例如,可能是通過PCI Express (PCIe)總線的系統交換信息等。探查串化器/解串器(SERDES)和PCIe控制器,使您能夠獲得底層協議層工作的詳細信息,這對于總線接口調試非常重要。但是,如果您希望總線接口能夠正常工作,觀察信息流,那么,您最好監視主存儲器中的緩沖,而忽略總線控制器。

問題的相對性

一旦找到了您需要的數據,確定了要在系統中的哪些地方來提取這些數據,那么,您需要收集數據,知道數據與時間的相關性,找到觸發模式,采集您希望保存的數據,從系統中提取出這些數據,送入分析工具中。在分立系統中,這一過程相對簡單:所有工作都可以回到邏輯分析儀中完成,分析儀提供統一時間基礎。在基于SoC的系統中,您可能希望把所有數據送回SoC的中心模塊中,如圖2所示。好消息是,泰克和ARM的IP簡化了這一過程。

圖2.完整的片內調試系統結合了傳統的CPU內核調試和數據采集站以及信息路由,提供將數據從芯片中輸出的方法。

但是,使用IP帶來了新問題。中心模塊和電路板另一側芯片之間的延時會有十幾個時鐘周期。即使在芯片內部,也會有數十個時鐘域,當您跨過時鐘域邊界時,延時會增加很多CPU周期。您怎樣知道兩路數據是同時的呢?

如果您要開發自己的調試工具,那么,這會很難。您可以估算數據采集模塊和中心控制器之間的傳播延時,然后,對數據流進行后處理,使其對齊。但是,這一方法難以解決時鐘域交叉的非確定性延時問題。您可以分配一路主時鐘,使用它對您采集的數據進行時間戳處理,但是,這需要很大的電路開銷。泰克等提供的商用解決方案同時使用了硬核IP和軟件算法,在底層自動完成所有這些工作。通過這些算法,可以在一個與時間相關的視圖中看到SoC不同時鐘域和不同物理位置上的事件,通常會發現意外的系統行為。

評論