采用FPGA的片上系統和嵌入式系統的遠程監控系統介紹

本系統立足于利用Intemet實現核環境信息的遠程采集。在實現上,采用了基于SOPC技術的嵌入式解決方案,通過在FPGA中嵌入NioslI軟核處理器和所需外設的IP Core(硅知識產權核),然后再配備相應的網絡接口,實現利用互聯網進行信息的傳輸。

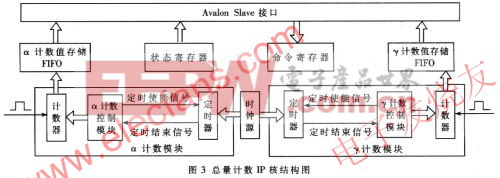

本文引用地址:http://www.j9360.com/article/148726.htm另外,通過開發用于控制信息采集子系統的IP核,利用FPGA固有的硬件并行特性,本系統做到了對多個信息源進行真正意義上的并行監控,即在進行α射線探測的同時也可以進行γ射線和溫濕度等信息的獲取。

1 系統硬件設計及實現

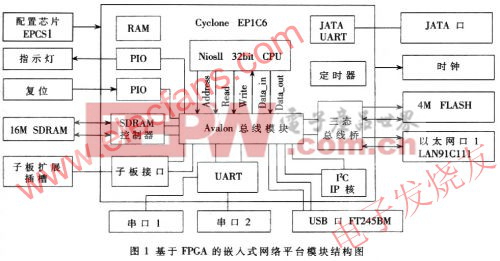

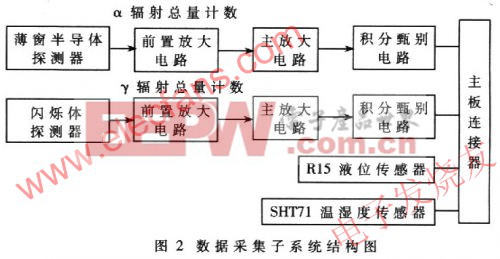

在本系統的設計中,硬件上為了做到通用性,在結構上劃分為兩部分,即用于完成現場監控和數據遠程傳輸的通用網絡平臺和用于完成溫濕度、液位、α及γ輻射總量測量等工作的環境信息采集子系統。其結構分別如圖l、圖2所示。兩個子系統通過一條40芯扁平電纜連接。在軟件上,考慮到利用互聯網進行遠程數據傳輸的復雜性,使用嵌入式操作系統和TCP/IP協議棧是必然的選擇,因此硬件上也圍繞這個關鍵點進行設計。

1.1 Niosii軟核CPU

NiosII軟核CPU是A137ERA公司推出的一種通用32位RISC嵌入式處理器,它特別為可編程邏輯進行了優化設計,并配備有功能完善的開發套件,包括C/C++編譯器、集成開發環境(IDE)、JTAG調試器等,是ALTERA公司可編程單芯片系統解決方案的核心。

作為一個軟核處理器,NiosII提供了可配置的硬件及軟件調試特性,包括基本的JTAG的運行控制(運行、停止、單步、存儲器等)、硬件斷點、數據觸發、片內和片外跟蹤、嵌入式邏輯分析儀。這些強大的工具可以在開發階段使用,調試通過后便可以去掉,節省資源。NiosII處理器還提供了高、中、低三種不同性能的內核,通過與ALTERA提供的超過60種IP核(UART、時鐘、DMA、SDRAM、并行I/0等)結合使用,設計師可以方便地針對特定的應用創建一個在處理器、外設、存儲器和I/O接口方面都完美的方案。除此以外,NiosII還有很多其他優秀的特性,如指令定制、硬件加速器等。

1.2 網絡接口單元

以太網接口芯片采用了SMSC公司專門用于嵌入式產品的LAN91C111快速以太網控制器。該芯片內部同時集成了以太網介質訪問控制器(MAC)及物理層收發器(PHY),支持10/100M全雙工傳輸模式、自動協商及流控等功能。其主機接口具有同步總線、異步總線等多種工作模式,可以方便地與各種體系的CPU連接。本設計中使用了異步總線接口模式,并與FLASH共用地址線和數據線,通過FPGA上的適配模塊連接到Avalon片內總線。

1.3 存儲器單元

由于存儲操作系統內核、應用程序代碼、程序數據等的需要,本系統使用了一片型號為AM29LV320D的FLASH芯片。該芯片由AMD公司推出,容量為4MB,支持CFI接口,其與AvMon總線的連接需要FPGA內部的總線適配模塊進行時序匹配。SDRAM用于存儲運行期的程序代碼和數據,HY57V563220B(L)T為現代公司推出的容量達16MB的SDRAM,由于該芯片端口寬度可達32位,因此系統中使用單芯片即可。SDRAM讀寫時序比較復雜,需要在FPGA中集成專用的SDRAM控制器IP核與其對接。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論