基于Nios II的Boost型功率因數校正系統研究

摘要:分析了基于雙環Boost型功率因數校正(PFC)的控制原理及小信號模型,建立了基于PI調節的Boost型PFC控制系統。由于現場可編程門陣列(FPGA)可將Nios II軟核處理器及PWM等外設集成到系統主控芯片,從而使系統具有控制精度高、可靠性好等優點。在此基礎上,設計了基于Nios II的Boost-PFC硬件電路,并搭建了相應的實驗平臺進行系統實驗。實驗結果表明,該系統校正后的功率因數高,達到了理論設計要求。

關鍵詞:功率因數校正;數字控制;現場可編程門陣列

1 引言

PFC技術是減小諧波污染問題的有效方法之一。將PFC技術與數字控制技術相結合,實現數字化的PFC控制系統,已成為電力電子技術的一個重要研究方向。隨著微電子和半導體生產工藝的提高,多數集成電路設計已進入片上可重構系統時代,從而使計算機進入微控制領域成為現實。在此基礎上,新型電力電子功率器件不斷出現,使得采用全控制的開關功率元件進行PWM控制方式成為主流。傳統PWM控制大多采用單片機及高性能的DSP來實現,但由于單片機內部系統體系結構和計算功能等條件有限,使其在實現高效控制算法等方面遇到了困難。而DSP需要使用大量的外圍電路,并且系統的可升級性較差。

EDA技術不斷發展,使得基于FPGA的數字系統為PFC系統的控制提供了一種新的有效方法。該方法就是在PFC系統中,將Nios II及PWM等外設集成到系統主控芯片EP2C8Q208C8型FPGA內,使得系統體積更小,成本低,可靠性高,更適合嵌入式系統的要求,而且具有現場可編程性,能夠進行升級換代,具有廣闊的應用前景。

2 Boost型功率因數校正系統原理及建模

2.1 系統總體控制方案

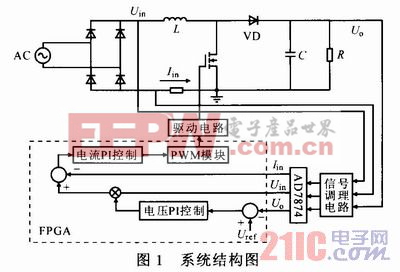

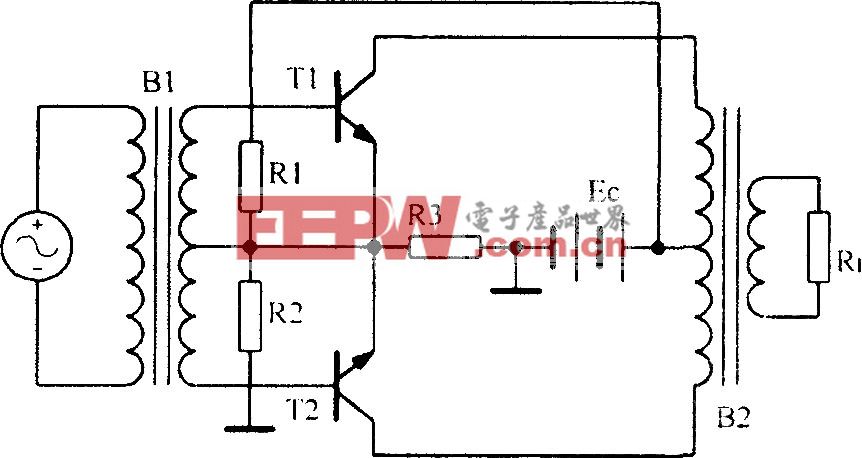

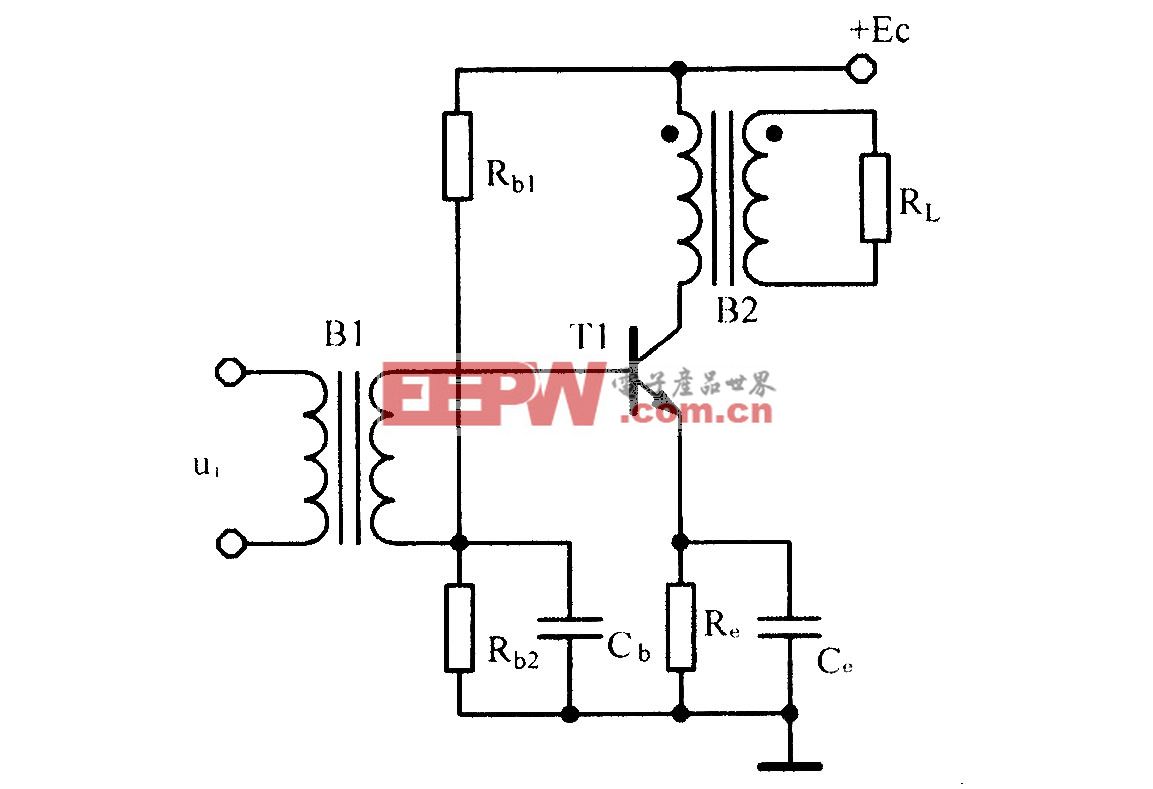

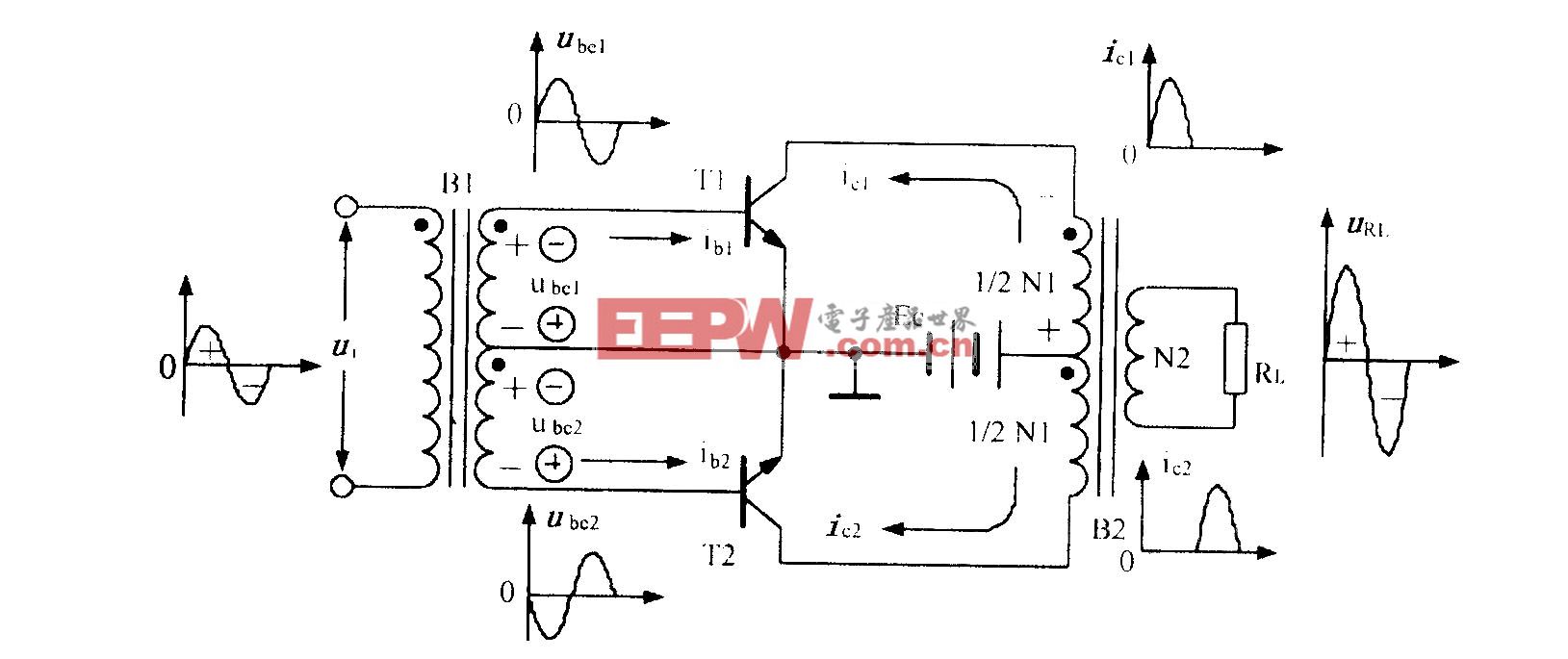

Boost PFC電路是現在應用最廣泛的有源PFC電路,具有功率因數值高,總諧波失真小,效率高的優點。該系統采用平均電流控制方式,工作在電感電流連續狀態,開關管電流有效值小、EMI濾波器體積小,應用FPGA數字芯片,其相對較復雜的控制也能較好地實現。為實現控制策略,系統需檢測整流輸入電壓Uin,輸入電感電流Iin和直流輸出電壓Uo。瞬時信號Uin,Iin,Uo分別從主電路上得到檢測,并經信號調理電路送至AD7874的3條A/D轉換通道。經過數字化采樣后的Uo信號與輸出參考電壓信號Uref進行比較,信號差送入電壓外環的PI調節器。該環節傳遞函數的輸出與Uin采樣值相乘,生成電流內環所必需的參考電流值Iref。Iin經數字采樣后,與Iref進行比較,運算結果送入電流內環PI調節器。該PI調節器輸出送入PWM比較器,與三角波信號比較產生開關信號的占空比,最后通過驅動電路產生驅動信號控制開關管的通斷,實現電路的PFC,系統結構如圖1所示。

2.2 Boost PFC模型建立

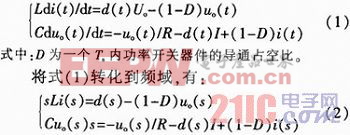

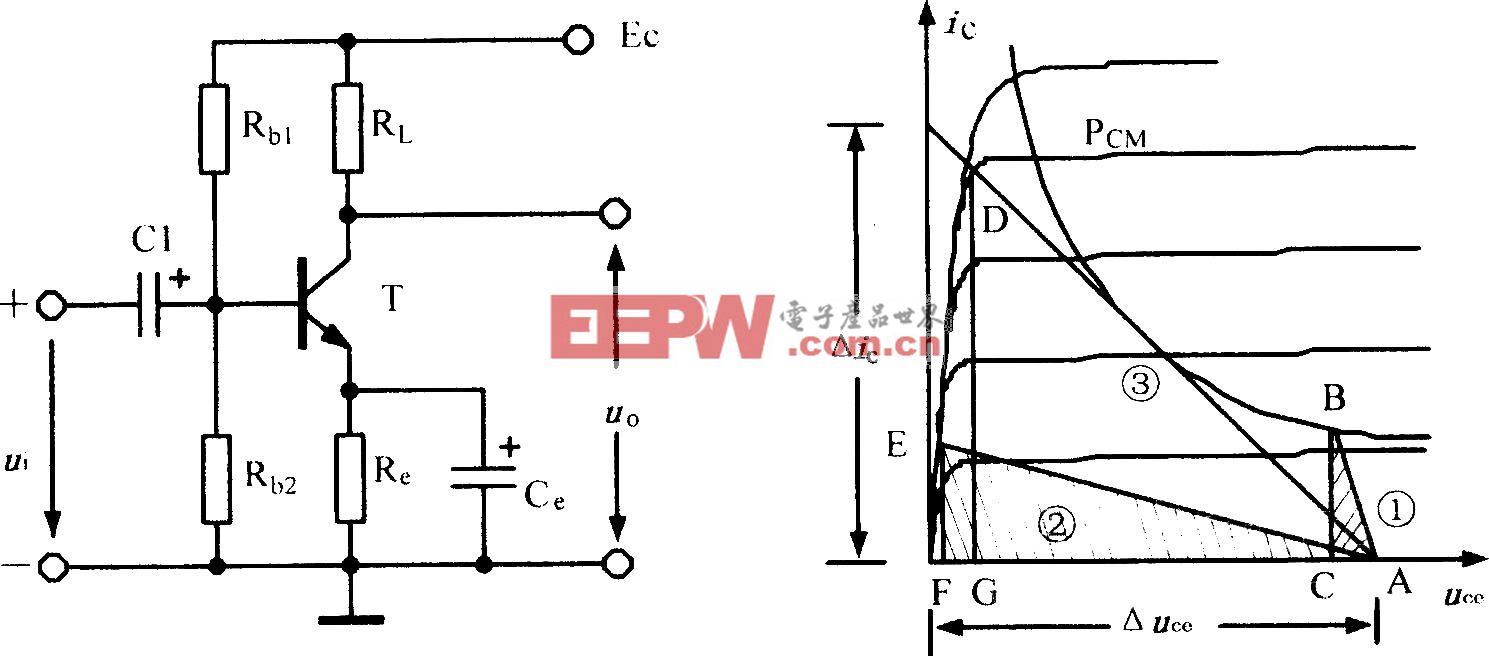

為實現Boost PFC的雙環PI數字控制,系統采用簡化的小信號模型建模。要得到Boost變換器的小信號模型,首先要得到平均法模型,然后進行小信號擾動分析。先分別對開關S導通時的電感電壓和開關S關斷時的電容電流進行積分,再除以周期Ts,即可得到它們在一個Ts內的平均模型,加入擾動并忽略高階項,可得該電路的動態小信號模型為:

式(2)中第1式中d(s)Uo,(1-D)uo(s),量很小;式(2)中第2式中d(s)I,(1-D)i(s)量很小,將其忽略,即可得到電感電流和輸出電壓對脈寬變化的傳遞函數:![]()

此處電壓環和電流環調節均采用經典PI調節器,其結構簡單,容易實現,將式(3)兩式進行Z變換可分別得到電流和電壓環的離散數學模

型,由此可根據系統要求分別求出電流環PI參數和電壓環PI參數。用VHDL語言在FPGA中編寫PI控制器程序,由于其軟件設計的靈活性,PI調

節參數能不斷得到修正和改進。

3 基于NiosⅡ的Boost-PFC硬件電路

主電路采用Boost拓撲結構,其特點為輸入電流連續,傳導噪聲低及良好的輸入波形。在主電路中,電流和電壓檢測采用霍爾元件實現,經處理后送入A/D采樣單元。驅動電路采用TLP250實現主電路與FPGA之間的隔離,保證了功率器件的可靠關斷。

3.1 NiosⅡ嵌入式硬件系統構建

EP2C8Q208C8型FPGA資源配置豐富,在該芯片上可嵌入Nios II軟核處理器。實驗證明嵌入的Nios II軟核主頻可平穩運行在120 MHz,可滿足PFC系統要求。

實驗采用QuartusII 9.0作為硬件開發平臺,利用SOPC Builder工具構建Nios II嵌入式硬件系統,SOPC Builder允許用戶選擇和自定義系統模塊的各個組件和接口。用戶可以很方便地將處理器、存儲器和其他外設模塊連接起來,形成一個完整的系統。在此先后將CPU,SDRAM模塊和EPCS控制器等IP核添加到系統中,從而構建了一個標準的Nios II最小系統。

最小系統建立后,根據PFC系統要求,還需定制PWM外設。在PFC系統中,系統經A/D前端處理及A/D轉換后送入Nios II中進行運算,其輸出再經過PWM比較器加到驅動電路上,以控制開關管導通和關斷,從而使輸入電流的波形與輸入電壓波形基本一致,使電流諧波減少,提高了輸入端的功率因數。在自定制PWM外設時,先用VHDL語言編寫PWM外設文件,編寫完畢后對代碼進行編譯和仿真。

驗證正確后,將其加入SOPC Builder中,做為Avalon外設,之后SOPC Builder生成整個Nios II嵌入式硬件系統。用Quartus II軟件編譯SOPC硬件系統,生成FPGA的配置文件,將其下載到開發板中的串行電可擦除Flash存儲芯片中,便完成了系統硬件平臺設計。

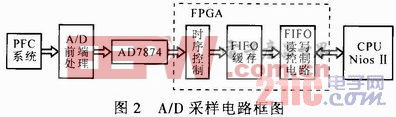

3.2 A/D采樣控制電路

在PFC系統中需采樣輸入電壓、輸入電流和輸出電壓3路實時信號,故需要3通道A/D轉換器,而AD7874是4通道12位同步數據采集器,其特性可滿足該系統要求,故選擇AD7874作為采樣控制器。在A/D采樣控制中,用Nlos II作為主處理器,主要完成數據和信息的收集和轉發功

能,用FPGA對采集的信號做預處理,并將數據存儲在高速FIFO中,從而實現數據的高速采集和目標提取,A/D采樣電路框圖如圖2所示。

4 軟件系統

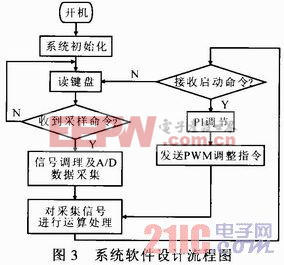

系統硬件平臺設計完成后,在Nios II 9.0 IDE軟件的開發環境中編寫系統嵌入式應用軟件,系統嵌入式軟件流程如圖3所示。

該系統中,Nios II程序的任務是在規定的控制周期內,通過預先設定的值得到控制任務及控制參數,同時接收A/D采樣控制電路的反饋信號,再經過CPU計算和處理后得到糾正的PWM控制參數并傳達給PWM模塊,最后由PWM模塊輸出相應的PWM信號以實現PFC系統的閉環PWM控制。

5 系統的實驗結果

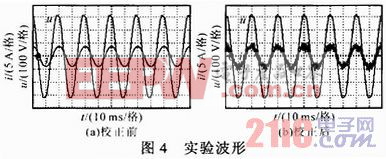

通過控制分析和參數確定,對用EP2C8Q208C8型FPGA作為主控芯片的數字功率因數校正器進行了實驗。此實驗交流輸入電壓為220 V/50Hz,功率器件開關頻率為30 kHz,輸出電壓經升壓后為380 V。用示波器分別測量了校正前、后的波形,結果如圖4所示。可見,輸入電流無論是波形還是相位都基本跟蹤了輸入電壓波形,功率因數達到0.98以上,得到了較為滿意的結果。

6 結論

此處主要圍繞PFC的數字化控制進行了研究,著重介紹了平均電流型Boost PFC電路,建立了平均電流控制電壓環、電流環的小信號數學模型,提出了設計思路,并設計了基于片上系統的數字控制方案,完成了實驗樣機的制作。測試結果表明,該系統控制精度高,功率因數值達到0.98以上,滿足了理論設計的要求,并驗證了此數字控制方案的可行性。

基于Nios II設計的PFC系統,設計周期短,集成度高,靈活性大,維護和升級方便,硬件缺陷修復和排除簡單,具有很好的移植性,用戶可根據需要對該模塊的設計思想進行修改。隨著科學技術的發展,采用嵌入式對PFC系統進行控制是一種新發展趨勢。

評論