一種I2C設備控制方法的設計和實現

1 引 言

本文引用地址:http://www.j9360.com/article/148259.htmI2C(Inter-Integrated Circuit)總線是由PHILIPS公司開發的兩線式串行總線,用于連接微控制器及其外圍設備。是微電子通信控制領域廣泛采用的一種總線標準。它是同步通信的一種特殊形式,具有接口線少,控制方式簡單,器件封裝形式小,通信速率較高等優點。AT91SAM7X256是Atmel公司于2005年推出的基于ARM7的工業級芯片,他以體積小、功耗低、連接方式廣泛、處理資源豐富、控制靈活等特點受到嵌入式領域開發人員的重視。本文介紹AT91SAM7X256的I2C控制器TWI接口(two-wired interface)的使用方法,并以I2C設備E2PROM和日歷時鐘芯片為例,實現AT91SAM7X256對時間數據的讀取與存儲。同時,為了驗證時間數據的讀取與存儲是否正確,使用AT91SAM7X256的在線仿真器J-LINK將E2PROM中的數據讀至內存進行檢查。

ARM(Advanced RISC Machines)是微處理器行業的一家知名企業,設計了大量高性能、廉價、耗能低的RISC處理器、相關技術及軟件。技術具有性能高、成本低和能耗省的特點。適用于多種領域,比如嵌入控制、消費/教育類多媒體、DSP和移動式應用等。ARM(Advanced RISC Machines)是微處理器行業的一家知名企業,設計了大量高性能、廉價、耗能低的RISC處理器、相關技術及軟件。技術具有性能高、成本低和能耗省的特點。適用于多種領域,比如嵌入控制、消費/教育類多媒體、DSP和移動式應用等。

2 硬件設計

2.1 硬件模塊結構

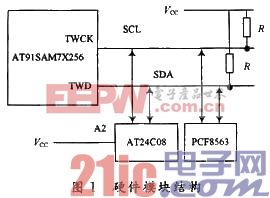

電路的硬件模塊結構如圖1所示。

AT91SAM7X256的TWI接口由一根時鐘線TWCK和一根數據線TWD組成,產生的信號時序符合I2C總線規范;PCF8563是Philips公司推出的一款內含I2C總線接口功能的工業級時鐘芯片;AT24C08是Atmel公司推出的符合I2C規約的兩線串口E2PROM.AT91SAM7X256的TWCK和TWD分別與芯片PCF8563和AT24C08的SCL與SDA相連,CPU通過TWI接口將時間數據讀出并存儲。為了保證CPU不沖突的訪問PCF8563和AT24C08,本文將AT24C08的A2管腳接高電平。由于I2C總線空閑時為高電平,所以為實現線與功能,總線上連接的設備均是集電極開路的,因此總線需外接上拉電阻R.AT91SAM7X256的TWI有主從2種工作模式,本文中AT91SAM7X256作為控制方,應工作于主模式。

2.2 AT91SAM7X256的TWI接口

AT91SAM7X256的TWD和TWCK管腳與設備的I/O管腳復用,同時AT91SAM7X256采用單獨控制功能單元的省電方案,電源管理單元PMC控制各功能單元的時鐘是否工作,所以要使用TWI接口,需要首先配置TWD和TWCK為外設連線和開路狀態,其次配置PMC使TWI時鐘處于工作狀態。

TWI接口可提供高達400 kb/s的傳輸速率,為使得數據的傳輸速率面向不同應用,可以通過配置時鐘脈沖發生器的控制寄存器TWI_CWEG調整TWCK的信號頻率。

TWI接口產生的信號時序符合I2C總線規范,當讀/寫1個字節數據時,主設備需提供從設備的設備地址、內部地址、讀寫控制以及起始標志和停止標志。在數據的收發過程中,主要使用控制寄存器TWI_CR、主模式寄存器TWI_MMR、內部地址寄存器TWI_IADR、狀態寄存器TWI_SR、傳輸保持寄存器TWI_THR和接收保持寄存器TWI_RHR.從設備地址在TWI_MMR中設置,從設備的內部地址在TWI_IADR中設置;在TWI_CR中設置是否發送起始信號和停止信號;NAK(無應答)、OVER(運行錯誤)、TXRDY(發送準備好)、RXRDY(接收準備好)、TX-COMP(傳輸完成)等狀態位通過查詢WI_SR得到。

寫數據的過程包括:當TWI_THR寫入數據后,CPU產生起始信號啟動傳輸,TWI_THR中的數據經過并串轉換后由TWD傳輸出去,當CPU收到從設備的應答信號后,TWI_SR的TXRDY將自動置1,說明數據已寫入從設備。讀數據的過程包括:CPU發出起始信號后,若TWI_SR的RXRDY位為1,則說明TWI_RHR中有數據等待接收,當TWI_RHR中的數據被讀出后,則RXRDY自動置為0.當讀/寫數據完畢后,CPU將產生一個停止信號結束傳輸,TWI_SR的TXCOMP將自動置1.

2.3 PCF8563日歷時鐘芯片的使用方法

按I2C協議規約,PCF8563具有惟一的設備地址0A2H.本文重點研究PCF8563時、分、秒數據的讀取方法,在此用到的內部寄存器包括控制/狀態寄存器1(地址為00H)、秒寄存器(地址為02H)、分寄存器(地址為03H)、小時寄存器(地址為04H)。由于寄存器中以BCD格式存儲時、分、秒數據,所以各時間時間寄存器的高位無效。

為使PCF8563工作于普通模式,需要將控制/狀態寄存器1置為00H,同時為了存儲正確的時間數據,需要將讀到的數據中無效的高位進行屏蔽。若需要校對時間,只需對時、分、秒寄存器進行寫操作即可。

2.4 AT24C08的使用方法

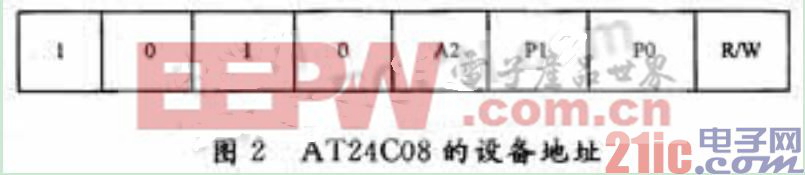

AT24C08是容量為8192 b(1024 B)的E2PROM.AT24C08內部分為4頁,每一頁有256字節單元,所以若要訪問某個單元則需要10位進行尋址,其中最高兩位是頁地址,低8位是頁內地址。設備地址的定義如圖2所示,其中P1P0對應頁地址,管腳A2可為AT24C08設定兩組設備地址。當A2為低電平時,4頁的設備地址分別為0A0H,0A2H,0A4H,0A6H;當A2為高電平時;反之為0A8H,0AAH,0ACH,0AEH.因此,為了避免AT24C08與PCF8563的設備地址沖突,需將A2連接高電平。

AT24C08的寫操作支持字節寫和頁面寫兩種方式。字節寫方式中每寫一個字節均需主設備提供起始信號、設備地址、內部地址以及停止信號;頁面寫方式即連續寫數據,需主設備提供起始標志、設備地址以及內部地址,數據全部寫完后再發送停止標志。

AT24C08的讀操作支持當前地址讀、隨機讀和順序讀3種方式。當前地址讀表示從當前內部地址單元讀出1個字節,所以主設備僅需提供起始信號、設備地址和停止信號;隨機讀表示從任意內部地址單元讀出1個字節,所以主設備需要先提供1次起始信號、設備地址、寫操作、設備內部地址和停止信號,設定設備的內部地址,之后再按當前地址讀方式讀數據即可;順序讀表示從當前地址開始連續讀多個字節,所以主設備需提供起始信號、設備地址、讀操作,數據全部讀完后再發送停止信號。

評論