基于多處理器的可識別方位引信信號處理系統

2 信號處理系統設計

2.1 功能要求

設計中定向探測引信的信號處理器是一個功能復雜的處理器,采用數字頻域處理方式實現,包括A/D轉換電路及信號處理模塊,實現對多普勒信號的采樣、量化,數字信號的FFT、CFAR處理,完成對目標的檢測、啟動判斷、干擾判別。其功能包括:(1)對4路多普勒信號進行數字化。(2)依據4路多普勒信號,實現時頻轉換及相關頻域處理。(3)在符合目標檢測判據時給出目標存在信號。(4)將多普勒信號的頻域峰值作為目標能量信息,對4路目標能量信息進行比較,實現引信周向8個象限的方位識別。

2.2 數宇信號處理系統工作原理

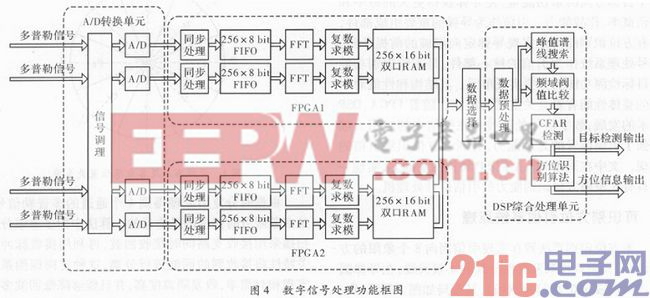

目標或環境回波經過引信接收前端,根據分時掃描原理得到4路多普勒回波,4路信號同時輸入信號處理電路。4路多普勒信號首先經過A/D采樣,形成回波時域數據,然后進行FFT頻域分析和坐標系轉換,基于線性逼近近似算法的求模運算、多處理器協同工作下的數據傳輸緩存,最終輸入DSP芯片中進行目標檢測和方位識別,得如果滿足一定的信噪比則給出目標存在信號,在目標存在的前提下繼續進行目標方位識別,輸出目標方位信息。設計信號處理系統采用了FPGA+DSP架梅,由FPGA完成4路FFT運算,由DSP完成目標檢測、脫靶方位識別,由2片FPGA芯片和單片DSP芯片梅成了一個多處理器協同工作的數字信號處理機。圖4給出了本設計中引信信號處理單元的流程框圖。本文引用地址:http://www.j9360.com/article/148047.htm

2.3 FPGA單元設計

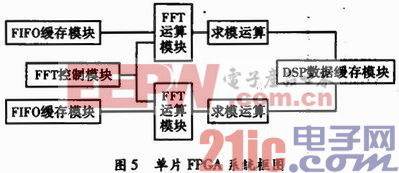

引信信號處理系統中兩片FPGA芯片,主要實現4路多普勒信號的時頻域轉換以及頻域信息的預處理,要求4路并行處理。FPGA芯片選用兩片Altera公司的EP1K100QI208—2,分別記為FPGA1和FPGA2,單片FPGA進行兩路FFT運算、求模運算以及計算結果的緩存。模塊化思想能夠大幅優化數字信號處理系統設計,增強代碼的可讀性和維修性,設計中廣泛采用了模塊化設計思想,對信號處理中的各項功能合理劃分。單片FPGA內部主要包含FIFO緩存模塊、FFT時頻轉換模塊、求模運算模塊、DSP數據緩存模塊。圖5為單片FPGA內部系統框圖。

評論