S2C在SoCIP2013研討會上展示高速SoC原型驗證硬件K7 TAI邏輯模塊

S2C(思爾芯)主辦的SoCIP2013研討會5月23日在北京舉行。Algotochip、Cadence、CAST等廠商出席并發表了演講。

本文引用地址:http://www.j9360.com/article/145820.htmS2C董事長及首席技術官陳睦仁分析指出,基于FPGA的原型驗證是成功設計SoC產品的關鍵步驟,然而,目前大多數項目經理仍把基于FPGA的原型驗證作為與主要設計和驗證流程分開的單獨過程。其結果是,需要額外的資源和時間在很短的時間內建立原型平臺。

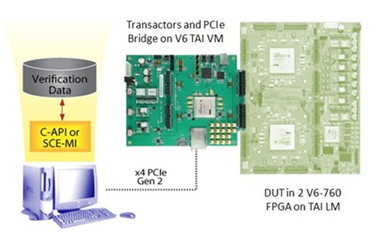

隨后,他介紹了采用S2C的整套開發工具,包括V7 TAI邏輯模塊,用于FPGA原型編譯和調試的TAI Player Pro軟件,及用于聯合建模的ProtoBridge系列DPI、C-API和SCE-MI軟件,將基于FPGA的原型驗證過程集成到從IP開發、模塊級驗證、仿真加速、SoC驗證到軟件開發的整個SoC設計和驗證流程中的方法。目的是縮短SoC設計周期。

S2C還在研討會現場展示了準備在6月3-6日于美國設計自動化大會(DAC)上展示的第五代原型驗證硬件K7 TAI 邏輯模塊系列。該系列產品基于賽靈思(Xilinx)的28nm Kintex7 FPGA。可在單板上提供410萬個ASIC邏輯門容量;有432個外部I/O;通過兩個高速差分I/O連接器,可實現16路、10Gbps的GTX收發器;60多個Prototype Ready接口;如需更高容量,可堆疊或并排互連幾個K7 TAI 邏輯模塊。

陳睦仁表示,S2C方案不僅采用賽靈思的FPGA技術,也有Altera的FPGA。因為這兩家廠商分別在隔代工藝節點上各領風騷,這樣可保證S2C在每一代工藝上都能選擇性能最好的FPGA技術。

Algotochip在演講中介紹了把C代碼算法直接生成GDS II文件的“藍盒子”技術。

在ARM和x86等主流嵌入式處理器架構盛行的今天,一些市場應用仍離不開“年邁的”8051處理器。IP提供商CAST介紹了沒有特許使用費的8051MCU核,及基于32位RISC架構的BA2x處理器系列。BA2x處理器的編程代碼的效率較高,在代碼和存儲器方面,該系統的芯片面積比8051系統更小。因此,可滿足8位8051用戶需要更多處理功能的需求。

評論