高性能數字接收機FPGA設計

摘要:基于Xilinx FPGA設計出一種高性能數字接收機。該數字接收機由高速、高分辨率A/D和高性能FPGA構成。高速A/D實現中頻數字化,高性能FPGA實現數字下變頻、數字多相濾波、半帶抽取、匹配濾波和位同步功能,使得中頻載波為153.6MHz的TD-SCDMA信號,下變頻-抽取-濾波-位同步后得到高質量的采樣率為1.28MHz的基帶信號。在中頻放大器工作時,接收機的動態范圍達到84dB,即A/D有效分辨率到13bit,EVM小于1%,滿足TD-SCDMA綜測儀的測試用例要求。

本文引用地址:http://www.j9360.com/article/145039.htm引言

軟件無線電是近些年在移動通信領域中流行的一種通信系統設計架構。基本思想是:用軟件設計的方法構造一個開放性、標準化和模塊化的通用平臺,設計出具有高度靈活性、開放性的移動通信系統。

基于軟件無線電的設計思想,數字接收機是根據奈奎斯特帶通采樣定理(欠采樣原理)利用A/D轉換器將中頻(IF)信號數字化,并在數字域中采用IQ正交下變頻方法將載波信號移除,得到高采樣率的零中頻基帶信號,再經過多級濾波、抽取(下采樣)、匹配濾波、位同步等步驟將調制信號的采樣率降到合適水平給后級處理,以減輕DSP數據吞吐量的壓力。

本設計來源于國家科技重大專項“三模綜測儀”子項目開發的TD-SCSMA部分;該數字接收機主要完成目標是實現數字信號處理的多速率變換,采樣率從122.88MHz降低到1.28MHz,線性動態范圍優于84dB,IQ兩路信號帶寬為1.6MHz。

電路設計

數字接收機架構

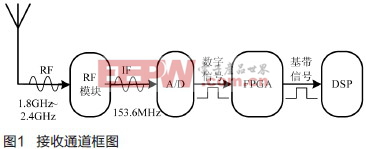

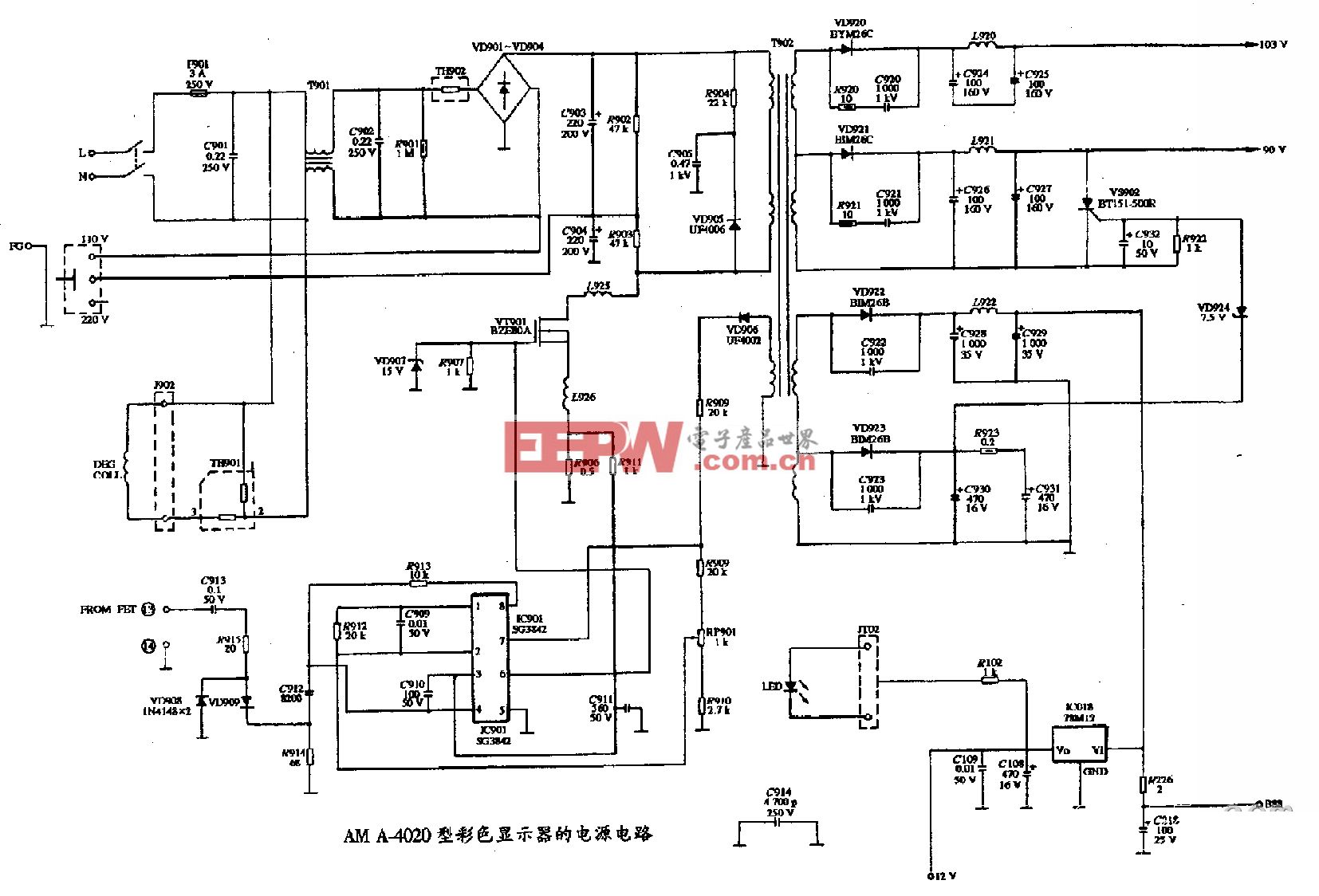

由于FPGA(XC5VSX95T)具備高速并行計算優勢,數字接收機方案設計通常由A/D轉換器+高性能FPGA+DSP構成。接收通道原理框圖如圖1所示。

移動終端的射頻范圍覆蓋1800MHz~2400MHz,射頻信號與本振信號混頻后,經過濾波轉變成固定載波頻率的153.6MHz中頻信號。根據帶通采樣定理,A/D以122.88MHz時鐘對153.6MHz中頻信號進行采樣、量化、編碼,數字化后的信號以122.88Msps速率傳輸給FPGA。最后在FPGA中實現30.72MHz的NCO與A/D發送的信號混頻以得到零中頻基帶信號,此時,數據的采樣率仍很高,需要進行多速率抽取濾波轉換、最佳采樣點的判斷和位同步處理。

數字下變頻原理

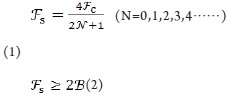

根據奈奎斯特帶通采樣(欠采樣)定理的公式:

其中,Fs表示A/D采樣頻率,Fc表示載波中頻頻率,B表示信號帶寬。

fpga相關文章:fpga是什么

pa相關文章:pa是什么

數字濾波器相關文章:數字濾波器原理

評論