驗證升溫,硬件仿真器成大規模IC設計新寵

2012年EVE被Synopsys收購,至此,三大EDA公司均涉足硬件仿真器。同時可見此市場整體呈上升的發展態勢。

本文引用地址:http://www.j9360.com/article/142790.htm 驗證為何上升快?

現在設計由很多IP幫助完成。隨著IP模塊化、功能復雜,做一個芯片越來越貴,甚至上百萬美元一次。如何保證設計出的芯片性能是理想的?驗證尤其是有質量的驗證的作用功不可沒。

“一次流片成功是最基本保證。你只要做過基本驗證,芯片基本會動作。”Mentor亞太區技術總監李潤華稱,“但是否按照你想象的去動作?我們經常看到這樣的現象,客戶早做出來芯片了,但遲遲推不到市場上,可能是硬件有缺陷,軟件正想辦法去彌補它。修改一次往往就是3~6個月時間。”

不像IC設計已經實現標準化了,驗證還沒有標準化,因此可以看到驗證還是較大的上升空間。另外,軟件在芯片中的比例和重要性上升,因為真正形成差異化的是軟件,每家公司有不同的軟件方法,哪怕運行在同一硬件平臺上,各家軟件還是有差異的。還有,每個IP的驗證也不是100%正確,假設每個IP有一個bug——約5%的缺陷,多個IP就是95%×95%×95%……,整個系統的缺陷就不可忽視。

三種仿真各有特點

仿真主要有三種手段:軟件仿真(simulation)、硬件加速仿真器和FPGA仿真。軟件仿真的特點是debug(調試)方便,但速度較慢,目前只有KHz級別。而FPGA仿真速度最快、價格較便宜,但不知哪里出了問題,像個瞎子,設計師要花很多時間找錯;而且容量一大,速度就掉下來了。硬件仿真加速器不僅仿真速度快(通常MHz級)、容量大,也可debug,但價格是三種中最貴的。

三種仿真方法市場并存,各有各的好處,不能相互替代。例如中小規模的IC設計可以采用軟件仿真;在初始仿真時,可以先用FPGA發現有問題;而中大規模或多地點設計團隊的更適合用硬件加速器。

Mentor硬件加速器滿足億門IC設計

Mentor于2012年4月推出了高速多功能硬件加速仿真器——Veloce。Mentor產品的優勢是首先有新的方法學——軟硬件協同設計;同時Mentor為Veloce專門設計的ASIC芯片有更大的容量,最大可容納5.12億門的ASIC設計,運行速度高達MHz級別;Mentor不僅推產品,還幫客戶搭建強大的驗證體系。

Mentor新的設計方法學強調軟硬件協同,其工具可以在單一環境知道硬件執行到哪一步,軟件執行到哪一行,RTL code在哪兒,因此調試效率高。在離線或異地Debug環境,通常效率不高;Mentor支持網絡訪問和多用戶系統,方法是硬件加速的結果可以放在服務器上,因此不同地點的軟件工程師直接取資料。

在驗證環境方面,Mentor本來擅長物理驗證,隨著Veloce的推出,Mentor環境可實現從功能到物理的所有驗證。通過并聯Veloce,還可以實現10億門及以上的設計。

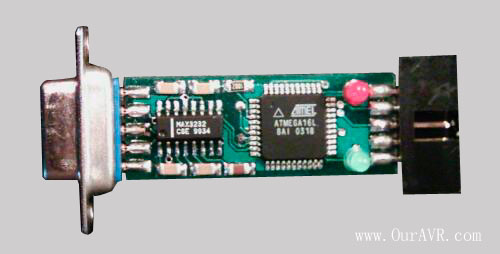

照片 Mentor的Veloce仿真器

評論